Research Interest

- Wireline Transceiver

- 5G Wireless Transceiver

- Optical Receiver

- High Speed A/D

- PLL

|

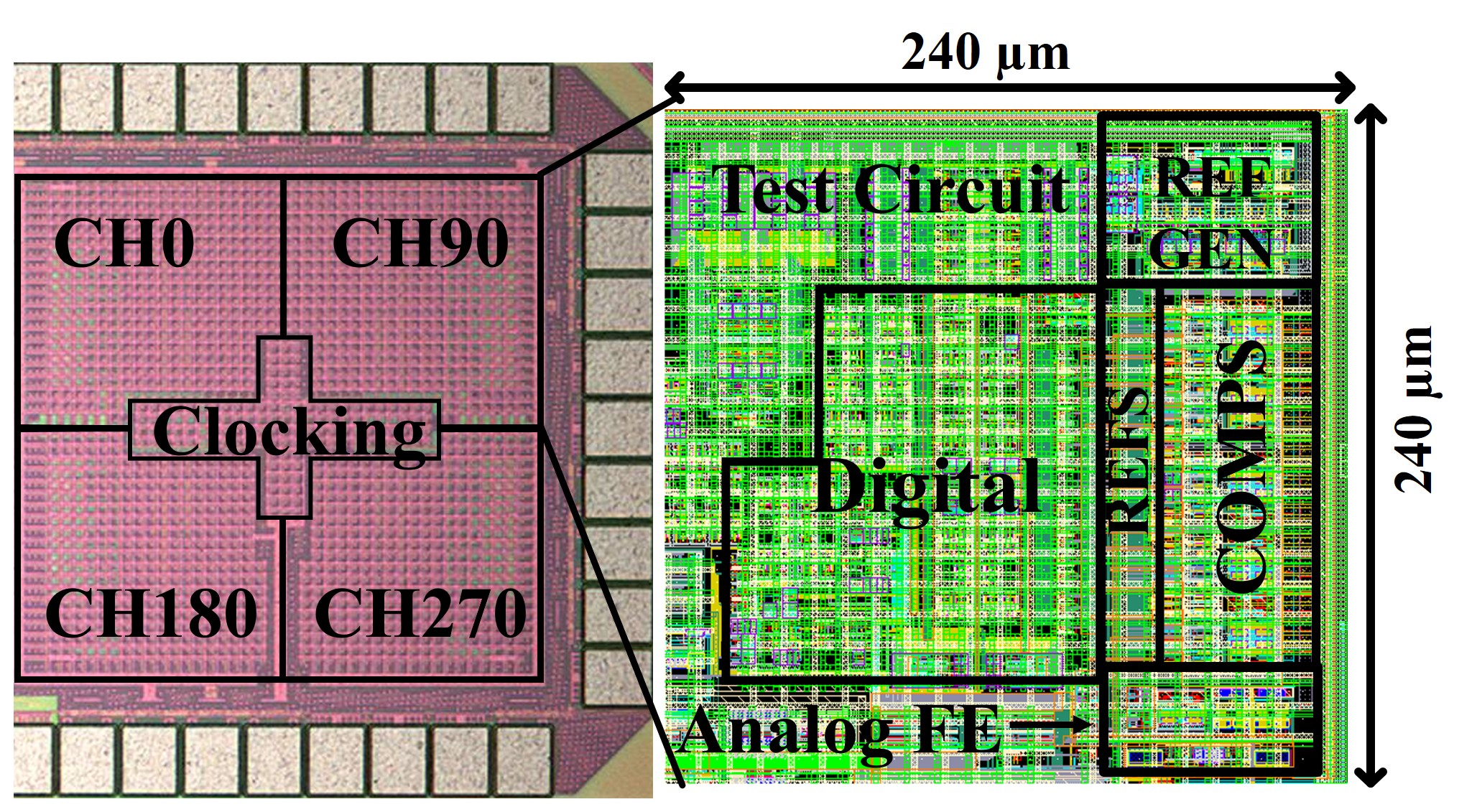

Direct Digital Sequence DetectorThis is an energy-efficient ADC-DSP less sequence detection and equalization. This scheme takes advantage of the ISI in the channel to reconstruct the time domain bit sequence. This concept is demonstrated with a 4-bit sequence decoder designed and fabricated in 65nm CMOS using only 4-data, 3-edge comparators. Consuming only 35 mW at 10 Gb/s and without any transmit equalization, this receiver is capable of compensating 27 dB channel loss with margin and 25 ps timing margin at BER of 10^-12. |

|---|---|

|

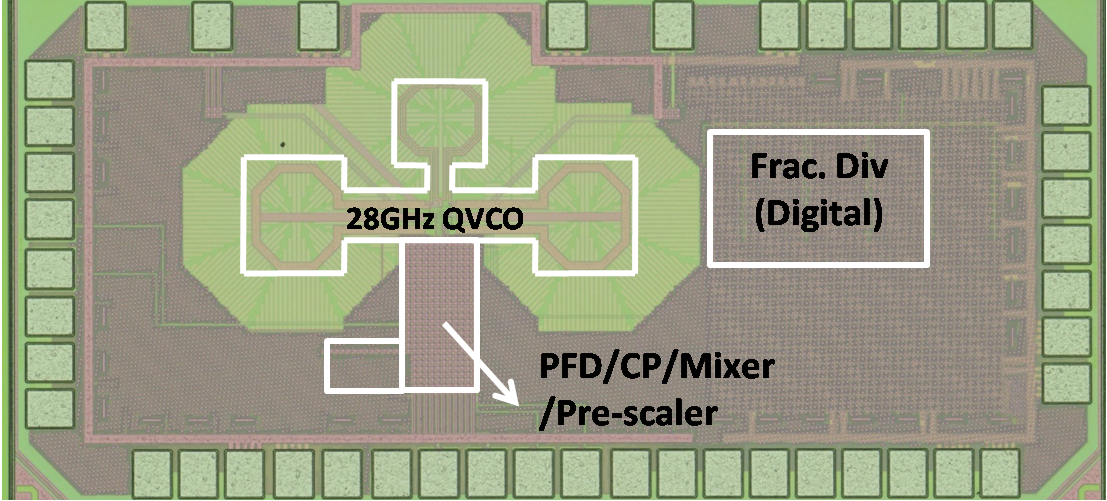

A Single Stage 28GHz Fractional-N Frequency Synthesizer for 5G Mobile Communications.A single stage quadrature 28GHz fractional-N Frequency synthesizer was implemented in the TSMC 65nm CMOS process. The fractional division is achieved using phase mixing. The implemented prototype occupies an active area of 0.18mm^2. |

|

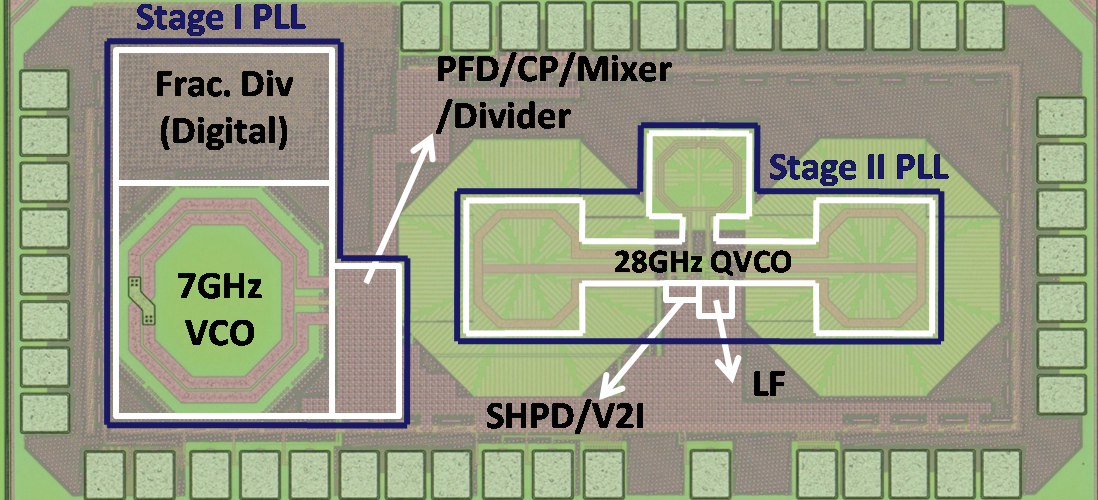

A Cascaded 28GHz Fractional-N Frequency Synthesizer for 5G Mobile Communications.A Cascaded quadrature 28GHz fractional-N Frequency synthesizer was implemented in the TSMC 65nm CMOS process. the first stage fractional PLL output is used to generate 7GHz clock which acts as reference for the following 28GHz quadrature sub-sampling PLL. The implemented prototype occupies an active area of 0.28mm^2. |