UNIVERSITY OF ALBERTA

LIBRARY RELEASE FORM

NAME OF AUTHOR: Philip Issa Kayal

TITLE OF THESIS: Tests of a Switched Capacitor Array for

the ATLAS Calorimeter

DEGREE: Master of Science

YEAR THIS DEGREE GRANTED: 1996

Permission is hereby granted to the University of Alberta Library to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly, or scientific research purposes only.

The author reserves all other publication and other rights in association with the copyright in the thesis, and except as hereinbefore provided, neither the thesis nor any substantial portion thereof may be printed or otherwise reproduced in any material form without the author's prior written permission.

---

Philip Issa Kayal

22 Wellington Ave.

Victoria, B.C.

V8V 4H6

**University of Alberta**

**Tests of a Switched Capacitor Array for the

ATLAS Calorimeter**

By

Philip Issa Kayal

A thesis submitted to the Faculty of Graduate Studies and Research

in partial fulfillment of the requirements for the degree of

Master of Science

Department of Physics

Edmonton, Alberta

Fall 1996

UNIVERSITY OF ALBERTA

FACULTY OF GRADUATE STUDIES AND RESEARCH

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research for acceptance, a thesis entitled "Tests of a Switched Capacitor Array for the ATLAS Calorimeter" submitted by Philip Issa Kayal in partial fulfilment of the requirements for the degree of Master of Science in

---

, Supervisor

---

---

Date: October 4, 1995

---

*to*

*my family*

## Abstract

This thesis describes an analog pipeline readout system that is being considered for the calorimeter of the ATLAS detector. Various tests have been performed on the switched capacitor array (SCA) chip, which is a crucial component of the analog pipeline readout system. In order to minimize the noise of the readout system, it is essential to know the noise of the various components of the system. The electronic noise of the SCA chip has been determined, and an analysis of the different contributions to the noise has been performed. When used in the ATLAS detector, the readout electronics will be subject to radiation. Thus, SCA chips have been exposed to electron, proton, and gamma radiation, and the performance of the chips under these conditions has been documented.

## Acknowledgements

I would like to thank Dr. Douglas M. Gingrich at the University of Alberta for supervising my research during the last two years.

The technicians at the Centre for Subatomic Research, University of Alberta, have done considerable work with SCA chips. In particular, I would like to thank Bill Burris, John Hewlett, Lars Holm, Shane Mullin, and Jan Schaapman.

I would like to thank Dr. Gordon R. Freeman and Dr. Yixing Zhao of the Department of Chemistry at the University of Alberta for the use of the Department's gamma irradiation facility, and also for performing Fricke dosimetry.

I wish to thank S.A. Kleinfelder of the Lawrence Berkeley Laboratory for access to the SCA chip design.

The members of the examining committee have my gratitude for their many useful comments.

Finally, I would like to thank all of my friends and colleagues for their support. Dugan O'Neil deserves special mention for his tireless contributions to the gamma irradiation experiment.

# Contents

|                                        |            |

|----------------------------------------|------------|

| <b>Abstract</b>                        | <b>iv</b>  |

| <b>Acknowledgements</b>                | <b>v</b>   |

| <b>Contents</b>                        | <b>vi</b>  |

| <b>List of Tables</b>                  | <b>xi</b>  |

| <b>List of Figures</b>                 | <b>xiv</b> |

| <b>1 Introduction</b>                  | <b>1</b>   |

| <b>2 Physics Motivation</b>            | <b>3</b>   |

| 2.1 Higgs Search . . . . .             | 3          |

| 2.2 Top-Quark Physics . . . . .        | 5          |

| 2.3 B-Physics . . . . .                | 7          |

| 2.4 Supersymmetric Particles . . . . . | 8          |

| 2.5 Summary . . . . .                  | 9          |

| <b>3 The Large Hadron Collider</b>     | <b>10</b>  |

| <b>4 The ATLAS Detector</b>            | <b>12</b>  |

| 4.1 The Inner Detector . . . . .       | 14         |

|          |                                          |           |

|----------|------------------------------------------|-----------|

| 4.2      | Calorimetry                              | 17        |

| 4.2.1    | Electromagnetic Calorimetry              | 20        |

| 4.2.2    | Hadronic Calorimetry                     | 23        |

| 4.3      | The Muon System                          | 24        |

| 4.4      | Triggering                               | 26        |

| <b>5</b> | <b>Calorimeter Electronics</b>           | <b>30</b> |

| 5.1      | Front-End Electronics                    | 30        |

| 5.2      | Readout Electronics                      | 33        |

| 5.3      | Digital Pipeline Approach                | 34        |

| 5.4      | Analog Pipeline Approach                 | 35        |

| <b>6</b> | <b>An Analog Pipeline Readout System</b> | <b>37</b> |

| 6.1      | Pipeline Readout Board                   | 37        |

| 6.1.1    | Switched Capacitor Array Chip            | 37        |

| 6.1.2    | Readout System Design                    | 38        |

| 6.2      | Pipeline Controller                      | 41        |

| 6.3      | System Architecture                      | 41        |

| 6.3.1    | Front-End Readout System                 | 45        |

| 6.3.2    | Remote Electronics                       | 47        |

| 6.4      | Previous Test Results                    | 47        |

|                                                                                                       |           |

|-------------------------------------------------------------------------------------------------------|-----------|

| 6.5 Present Work . . . . .                                                                            | 48        |

| <b>7 Noise Analysis</b>                                                                               | <b>50</b> |

| 7.1 Addressing Test . . . . .                                                                         | 54        |

| 7.2 Stray Capacitance and Bus Reset Tests . . . . .                                                   | 55        |

| 7.2.1 Individual Capacitors . . . . .                                                                 | 58        |

| 7.3 Board Modification . . . . .                                                                      | 62        |

| 7.3.1 Capacitor Uniformity Check . . . . .                                                            | 64        |

| 7.3.2 Voltage Drifting . . . . .                                                                      | 67        |

| 7.3.3 Summary . . . . .                                                                               | 67        |

| 7.4 Analysis of the Coherent and Incoherent Noise Components of the RD3<br>Calorimeter Data . . . . . | 67        |

| 7.4.1 Introduction . . . . .                                                                          | 68        |

| 7.4.2 Pedestal Data . . . . .                                                                         | 68        |

| 7.4.3 Coherent and Incoherent Noise . . . . .                                                         | 69        |

| 7.4.4 Entire System Analysis . . . . .                                                                | 69        |

| 7.4.5 Board Analysis . . . . .                                                                        | 73        |

| 7.4.6 Chip Analysis . . . . .                                                                         | 74        |

| 7.4.7 Conclusions . . . . .                                                                           | 77        |

| <b>8 Exposure of SCA Chips to Radiation</b>                                                           | <b>79</b> |

|          |                                                       |            |

|----------|-------------------------------------------------------|------------|

| 8.1      | Electron and Proton Radiation Effects . . . . .       | 79         |

| 8.1.1    | Introduction . . . . .                                | 80         |

| 8.1.2    | Observations . . . . .                                | 80         |

| 8.1.3    | Effects of Proton Irradiation and Annealing . . . . . | 80         |

| 8.1.4    | Effects of Electron Irradiation . . . . .             | 84         |

| 8.1.5    | Temperature Effects . . . . .                         | 86         |

| 8.1.6    | Death of a SCA Chip . . . . .                         | 86         |

| 8.1.7    | Conclusions . . . . .                                 | 88         |

| 8.2      | Exposure to Gamma Radiation . . . . .                 | 89         |

| 8.2.1    | Introduction . . . . .                                | 89         |

| 8.2.2    | Chip A . . . . .                                      | 91         |

| 8.2.3    | Chip B . . . . .                                      | 97         |

| 8.2.4    | Chip C . . . . .                                      | 104        |

| 8.2.5    | Chip D . . . . .                                      | 111        |

| 8.2.6    | Individual Cells . . . . .                            | 115        |

| 8.2.7    | Radiation Damage Mechanism . . . . .                  | 117        |

| 8.2.8    | Conclusions . . . . .                                 | 120        |

| <b>9</b> | <b>Summary</b>                                        | <b>125</b> |

|          | <b>Bibliography</b>                                   | <b>127</b> |

## List of Tables

|      |                                                                                                                                           |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.1  | The tests which have been performed on SCA chips. (CSR, UofA denotes the Centre for Subatomic Research, University of Alberta.) . . . . . | 49 |

| 7.1  | Number of events in each run. . . . .                                                                                                     | 50 |

| 7.2  | Results of noise analysis tests. . . . .                                                                                                  | 53 |

| 7.3  | Results of noise analysis tests, with the 18 noisiest capacitor addresses excluded. . . . .                                               | 56 |

| 7.4  | Number of events for each run in the stray capacitance test. . . . .                                                                      | 56 |

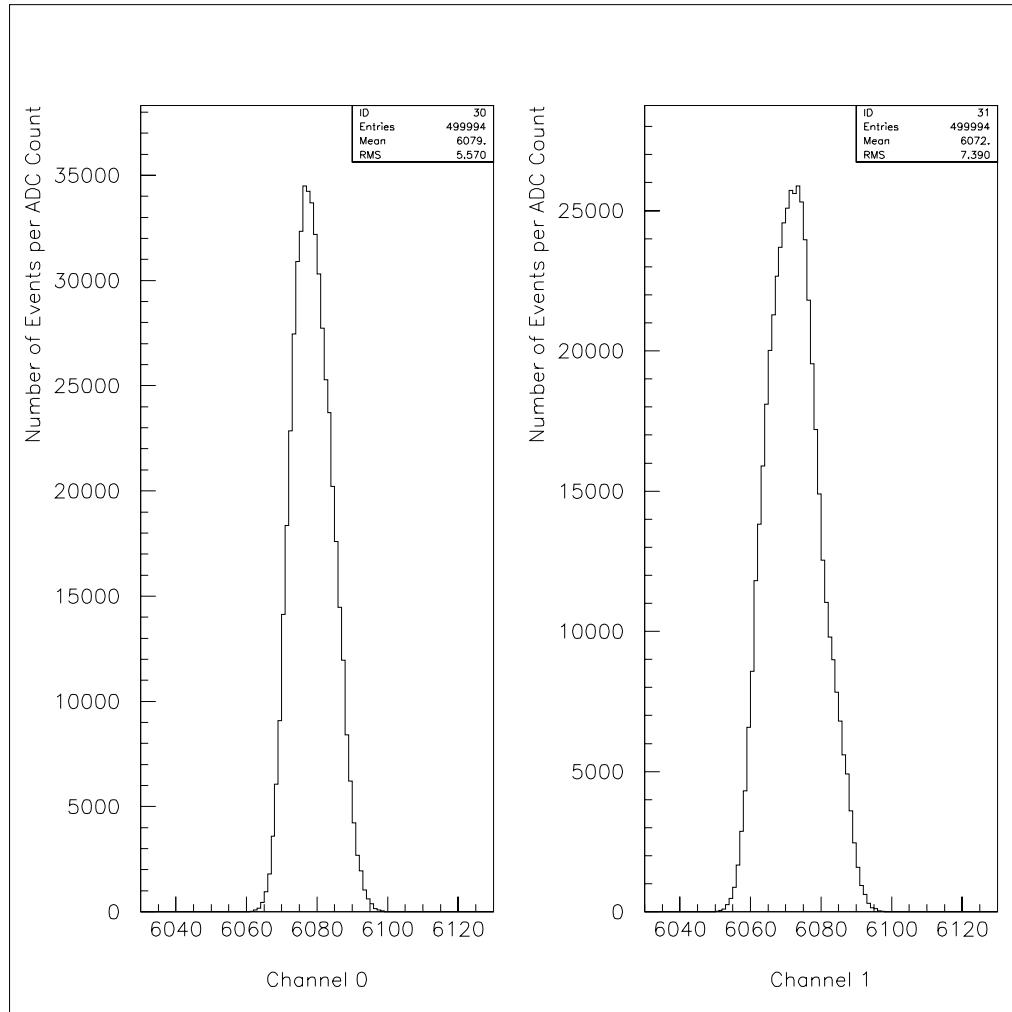

| 7.5  | Number of ADC counts and rms variation for both channels and all three runs in the stray capacitance test. . . . .                        | 57 |

| 7.6  | Number of events obtained for each capacitor. . . . .                                                                                     | 59 |

| 7.7  | Mean number of ADC counts and rms variation for Channel 0 - all three runs. . . . .                                                       | 60 |

| 7.8  | Mean number of ADC counts and rms variation for Channel 1 - all three runs. . . . .                                                       | 61 |

| 7.9  | Mean number of ADC counts and rms variation for both channels. . . . .                                                                    | 62 |

| 7.10 | Number of events in each of the five pedestal runs studied. . . . .                                                                       | 70 |

| 7.11 | Noise values for each run, averaged over time samples. . . . .                                                                            | 70 |

| 7.12 | Noise values for each time sample, averaged over runs. . . . .                                                                            | 72 |

| 7.13 | Global pedestal noise values, averaged over the eight time samples and five runs. . . . .                                                 | 72 |

|                                                                                                      |     |

|------------------------------------------------------------------------------------------------------|-----|

| 7.14 Averages across time samples for Run 1 - la0716.seq4. . . . .                                   | 73  |

| 7.15 Averages across time samples for Run 2 - la0719.seq7. . . . .                                   | 75  |

| 7.16 Averages across time samples for Run 1 - la0716.seq4. . . . .                                   | 75  |

| 7.17 Averages across time samples for Run 2 - la0719.seq7. . . . .                                   | 76  |

|                                                                                                      |     |

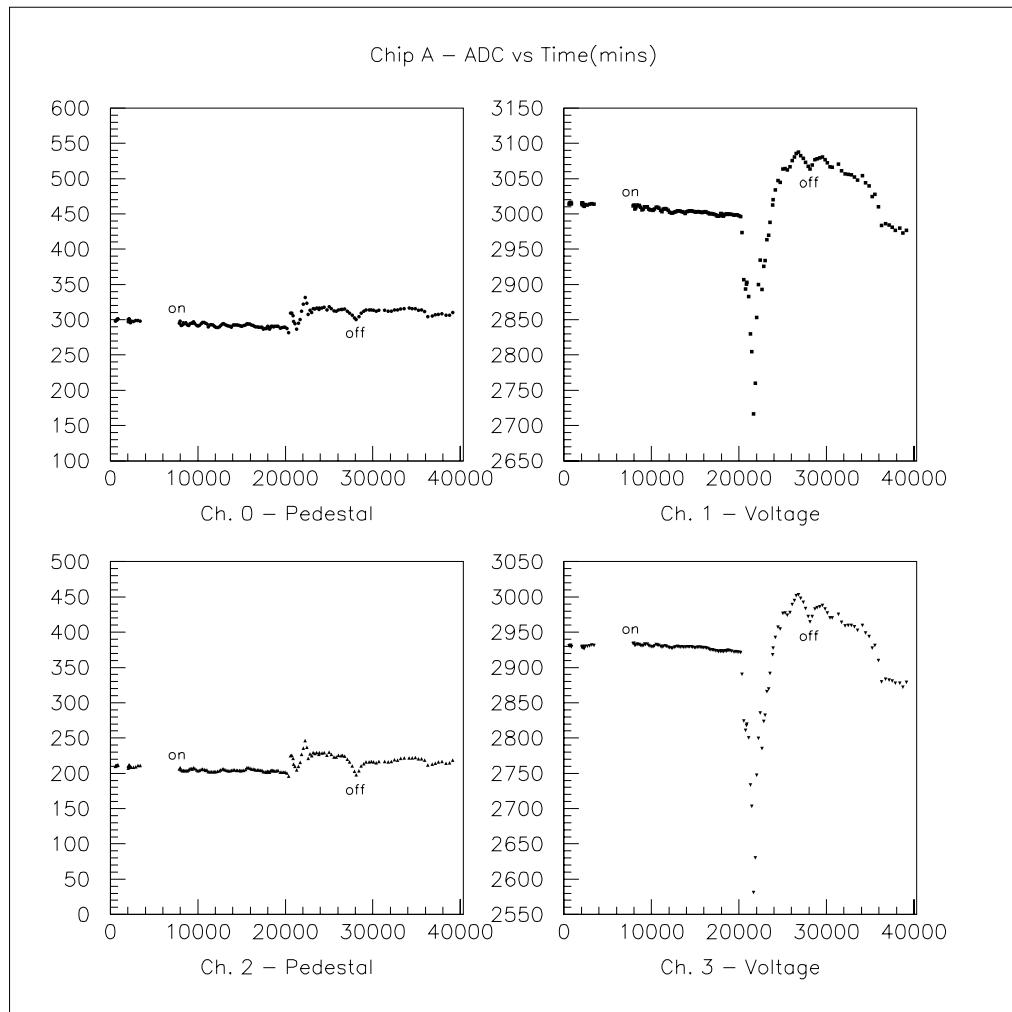

| 8.1 Number of ADC counts for all four channels at various points in the run,<br>for Chip A. . . . .  | 93  |

| 8.2 Minimum and maximum number of ADC counts achieved during the erratic period, for Chip A. . . . . | 96  |

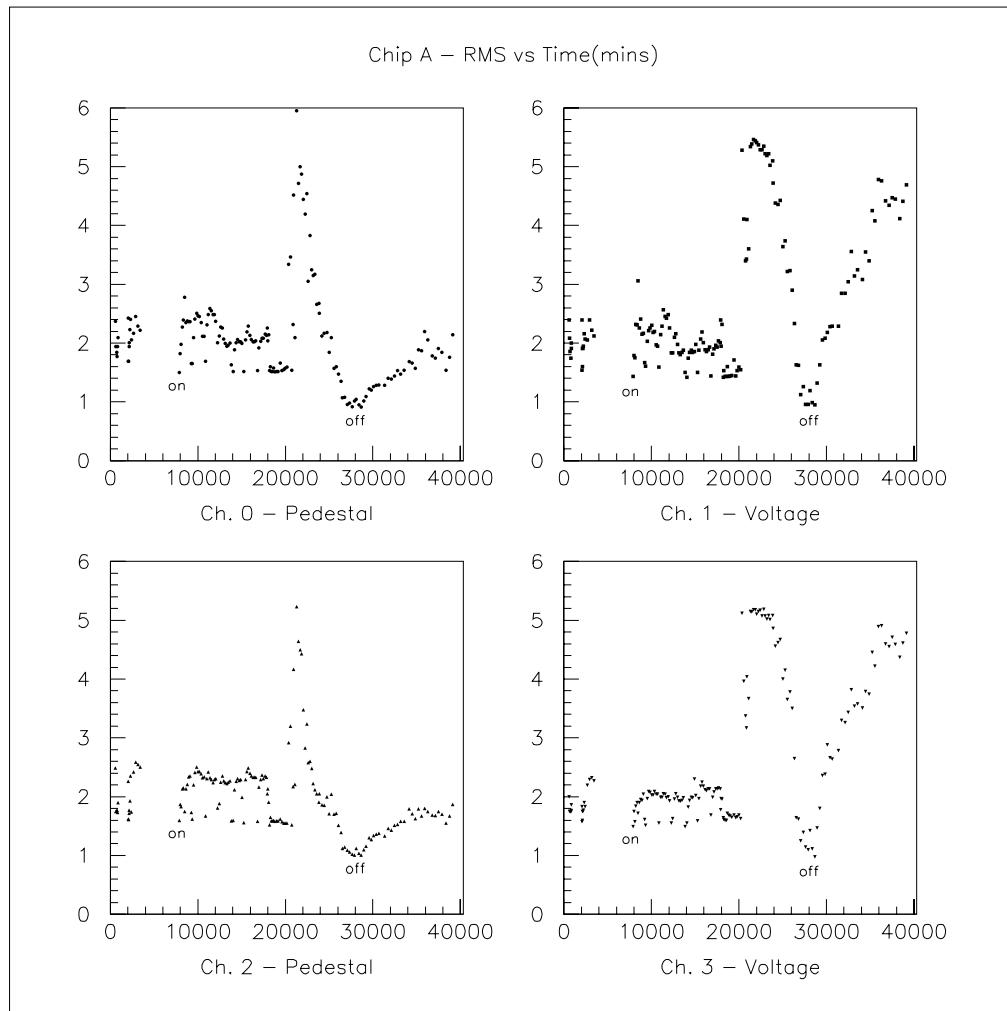

| 8.3 RMS noise in ADC counts for all four channels at various points in the run, for Chip A. . . . .  | 96  |

| 8.4 Minimum and maximum rms noise achieved during the erratic period, for Chip A. . . . .            | 100 |

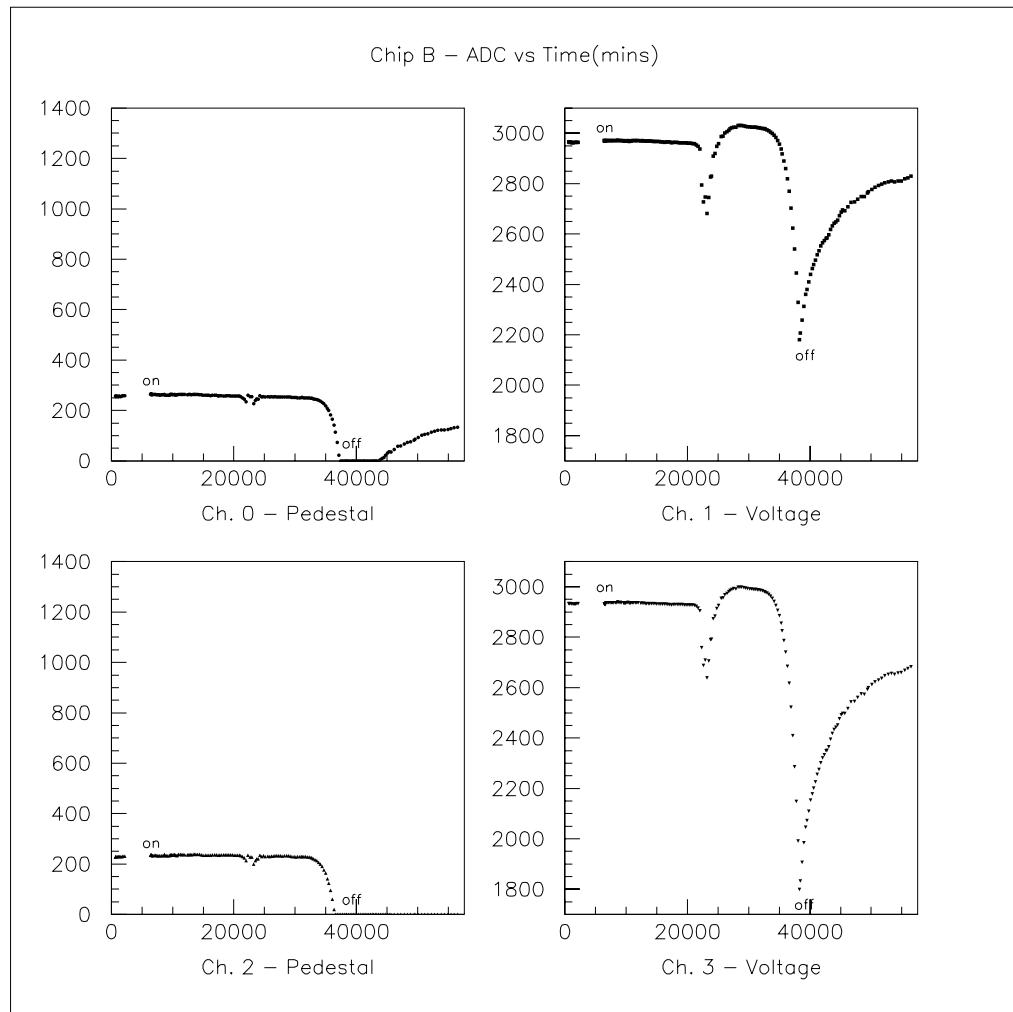

| 8.5 Number of ADC counts for all four channels at various points in the run,<br>for Chip B. . . . .  | 100 |

| 8.6 Minimum and maximum number of ADC counts achieved during the entire run, for Chip B. . . . .     | 103 |

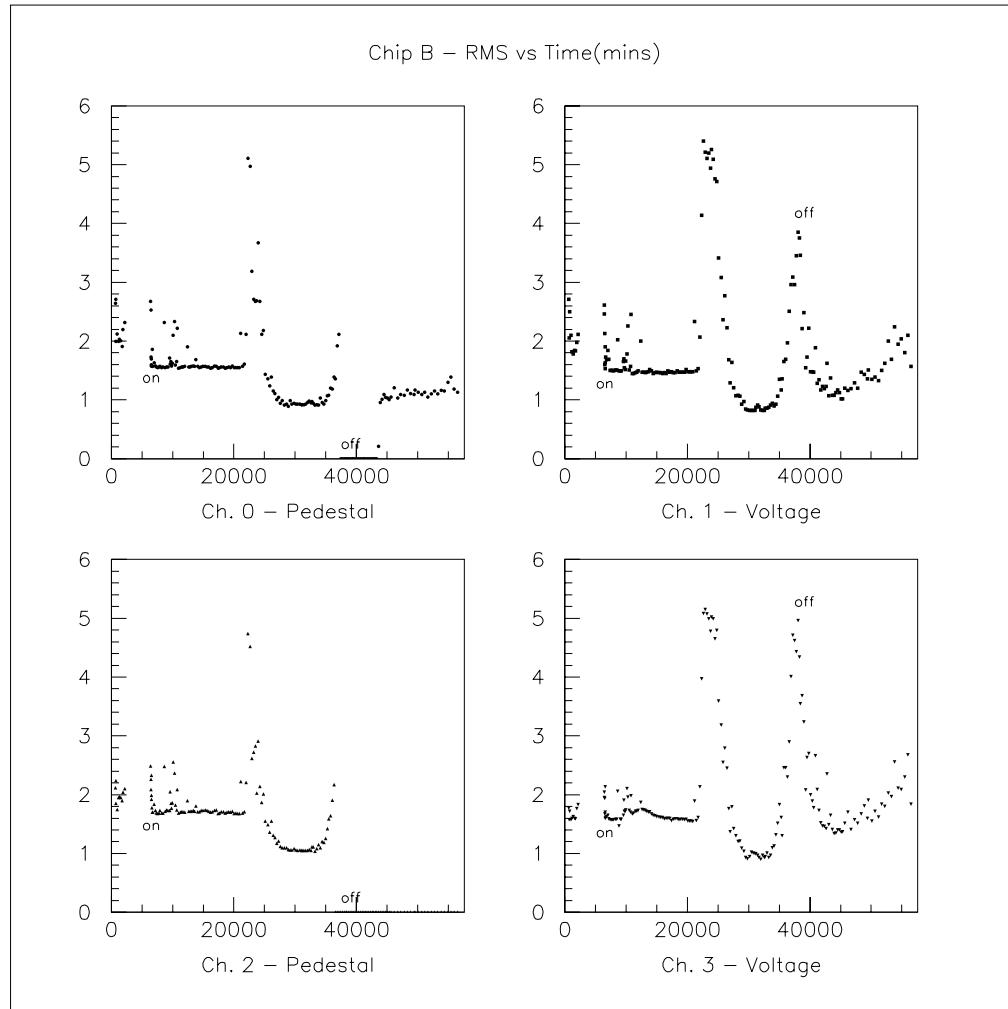

| 8.7 RMS noise in ADC counts for all four channels at various points in the run, for Chip B. . . . .  | 103 |

| 8.8 Minimum and maximum rms noise achieved during the entire run, for Chip B. . . . .                | 104 |

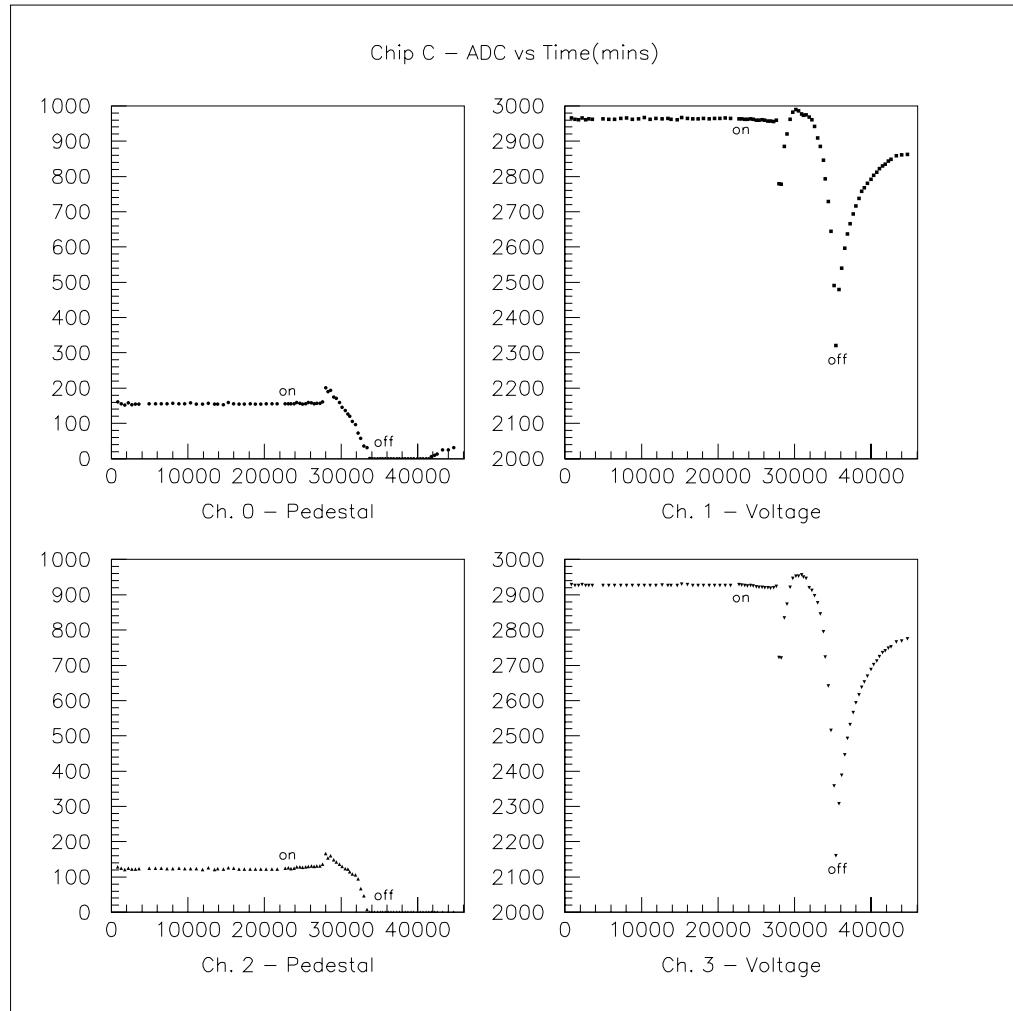

| 8.9 Number of ADC counts for all four channels at various points in the run,<br>for Chip C. . . . .  | 107 |

|                                                                                                      |     |

|------------------------------------------------------------------------------------------------------|-----|

| 8.10 Minimum and maximum number of ADC counts achieved during the entire run, for Chip C. . . . .    | 107 |

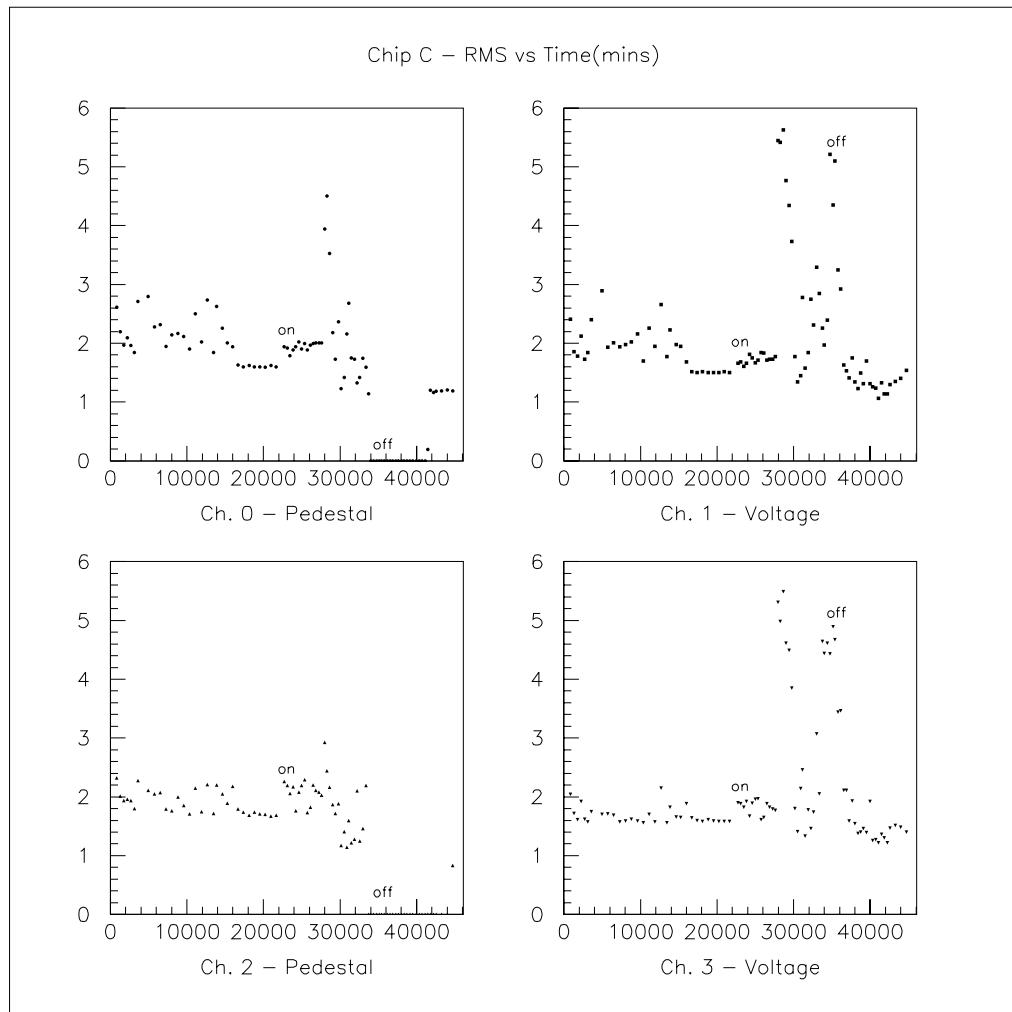

| 8.11 RMS noise in ADC counts for all four channels at various points in the run, for Chip C. . . . . | 110 |

| 8.12 Minimum and maximum rms noise achieved during the entire run, for Chip C. . . . .               | 110 |

| 8.13 Number of ADC counts for all four channels at various points in the run, for Chip D. . . . .    | 113 |

| 8.14 Minimum and maximum number of ADC counts achieved during the entire run, for Chip D. . . . .    | 116 |

| 8.15 RMS noise in ADC counts for all four channels at various points in the run, for Chip D. . . . . | 116 |

| 8.16 Minimum and maximum rms noise achieved during the entire run, for Chip D. . . . .               | 121 |

| 8.17 Results of the photon irradiation of SCA chips. . . . .                                         | 121 |

## List of Figures

|     |                                                                                                                                                                                                                      |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1 | The ATLAS detector. . . . .                                                                                                                                                                                          | 13 |

| 4.2 | Three-dimensional cutaway view of the ATLAS Inner Detector (taken from the ATLAS Technical Proposal, 1994). . . . .                                                                                                  | 16 |

| 4.3 | Three-dimensional view of the ATLAS calorimeter system (taken from the ATLAS Technical Proposal, 1994). . . . .                                                                                                      | 18 |

| 4.4 | Exploded view of the tube electrode structure of the forward calorimeter (taken from the ATLAS Technical Proposal, 1994). . . . .                                                                                    | 20 |

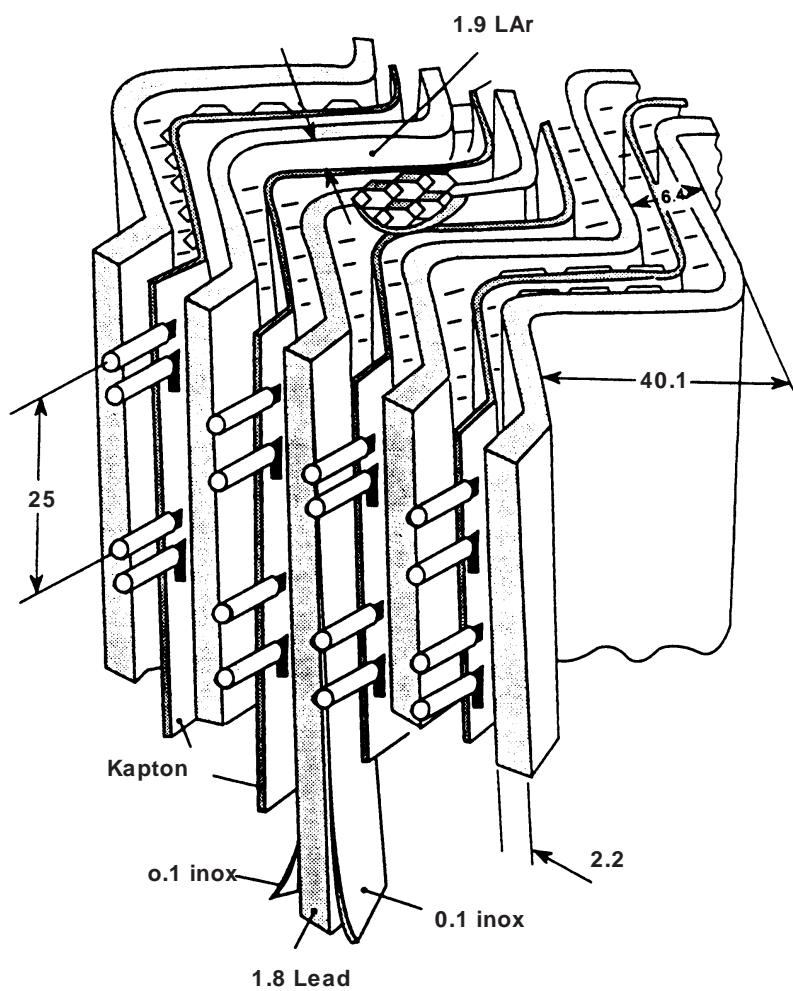

| 4.5 | Artist's view of an accordion calorimeter. . . . .                                                                                                                                                                   | 22 |

| 4.6 | Side view of the detector, showing the position of the muon chambers (taken from the ATLAS Technical Proposal, 1994). . . . .                                                                                        | 27 |

| 4.7 | Schematic of the muon trigger in the barrel and end-cap (taken from the ATLAS Technical Proposal, 1994). . . . .                                                                                                     | 27 |

| 4.8 | The ATLAS three-level trigger architecture (taken from the ATLAS Technical Proposal, 1994). . . . .                                                                                                                  | 29 |

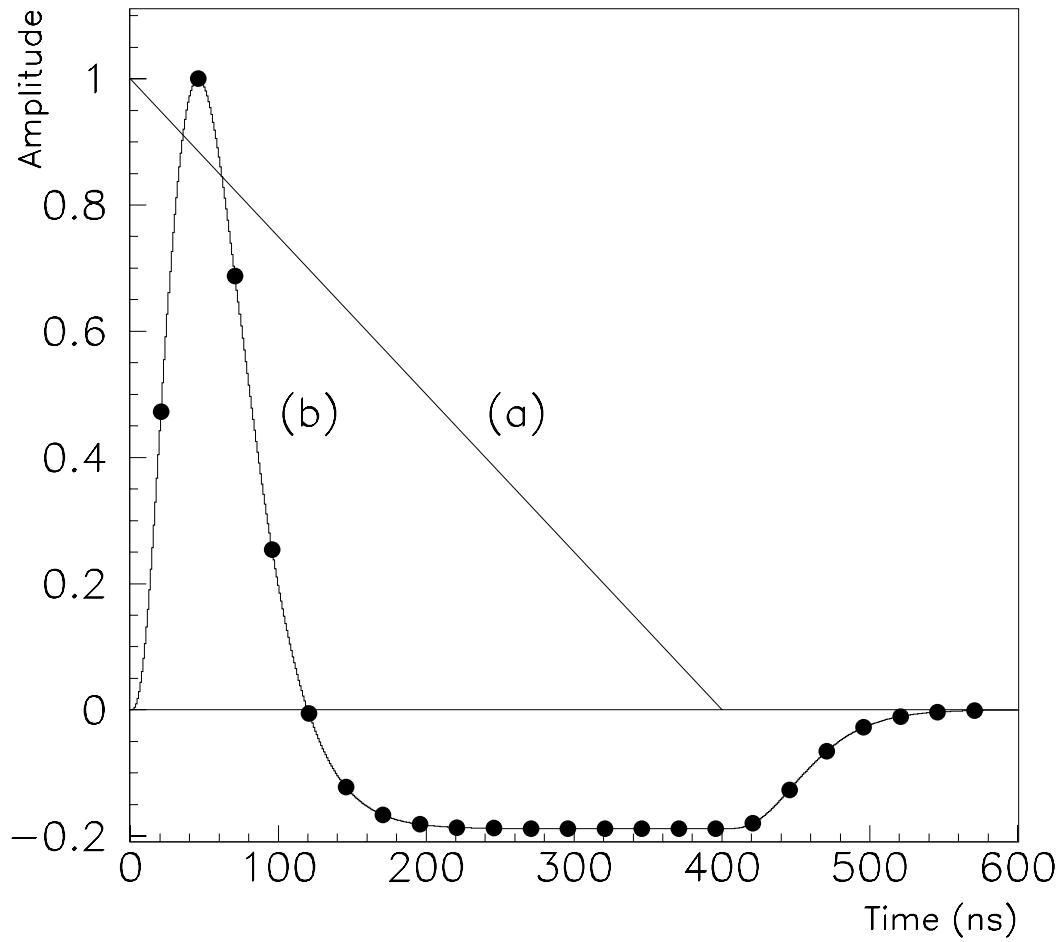

| 5.1 | (a) Drift current versus time for an ionization calorimeter; (b) Response of a bipolar shaper with a shaping time of 20 ns. The dots indicate the beam crossings. (Taken from the ATLAS Technical Proposal, 1994). . | 32 |

| 6.1 | A simplified block diagram of an analog memory cell structure (taken from M. Levi <i>et al.</i> , "A Switched Capacitor Array Based System for High-Speed Calorimetry", 1991). . . . .                               | 39 |

|     |                                                                                                                                                   |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.2 | Schematic diagram of 16 channels of the readout system design. The timing, control logic, and Level 1 trigger connections are not shown. . . . .  | 40 |

| 6.3 | Plot of deadtime (as a percentage) versus trigger rate (kHz), for different numbers of samples (s) and different readout times ( $\mu$ ). . . . . | 42 |

| 6.4 | Block diagram of the address list processor design. . . . .                                                                                       | 43 |

| 6.5 | Basic concepts of the readout architecture. . . . .                                                                                               | 44 |

| 6.6 | Layout of the pipeline readout boards. . . . .                                                                                                    | 46 |

| 7.1 | Histograms of ADC counts for pedestal-subtracted voltage data (both channels. . . . .                                                             | 63 |

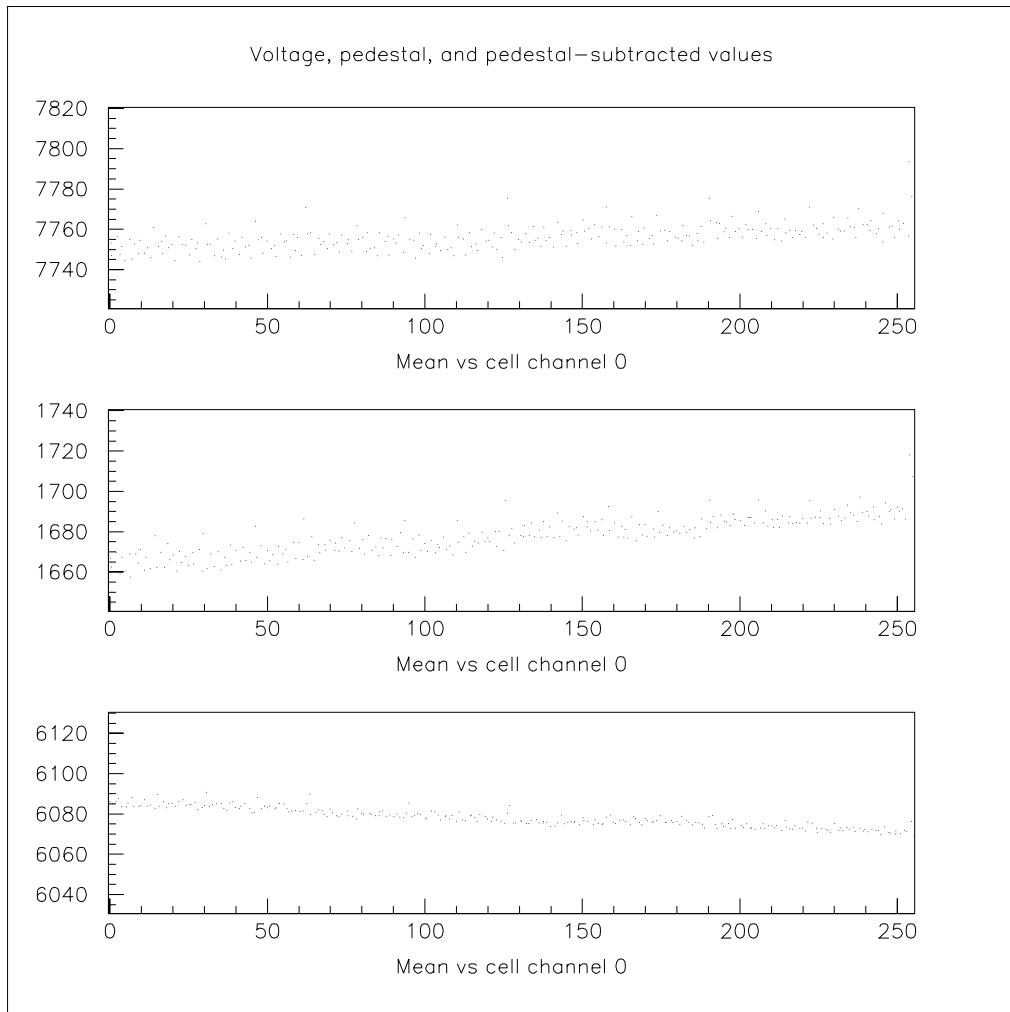

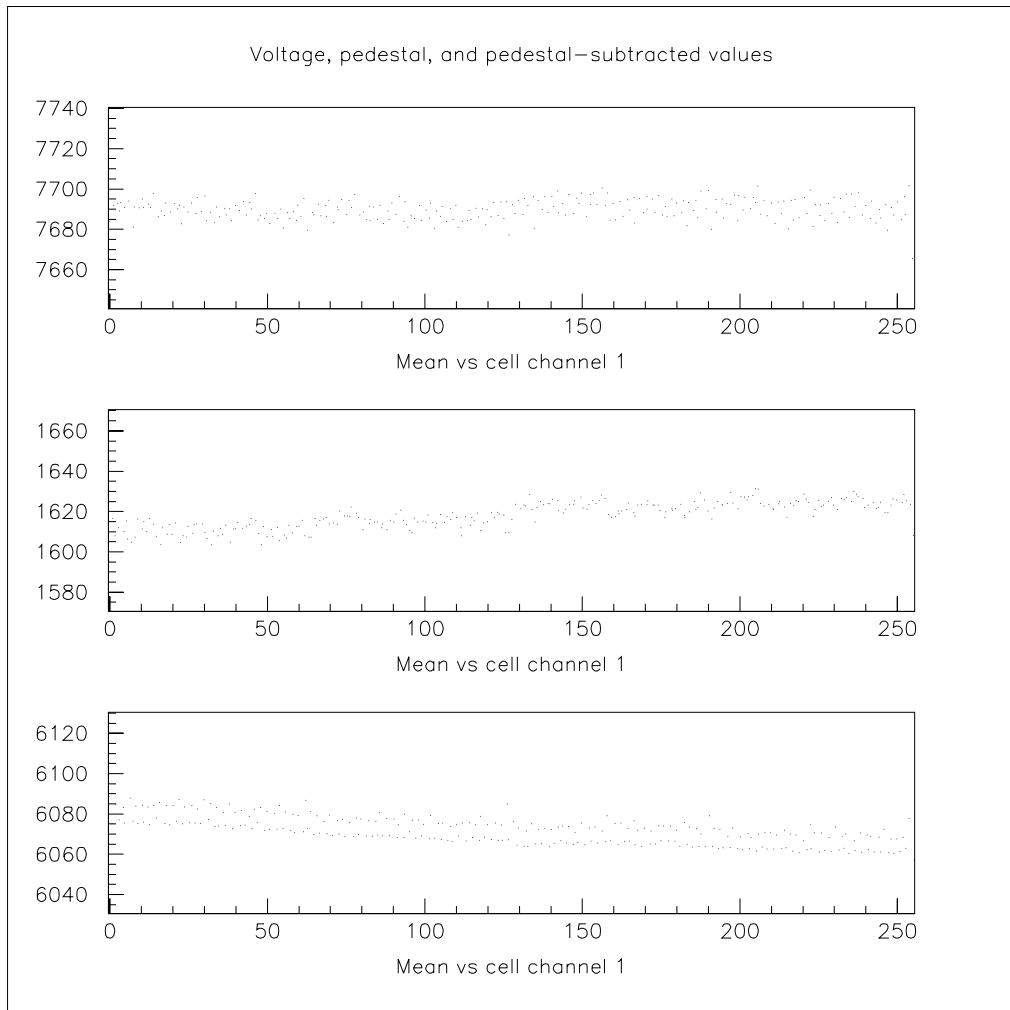

| 7.2 | Mean ADC counts versus capacitor address for Channel 0. . . . .                                                                                   | 65 |

| 7.3 | Mean ADC counts versus capacitor address for Channel 1. . . . .                                                                                   | 66 |

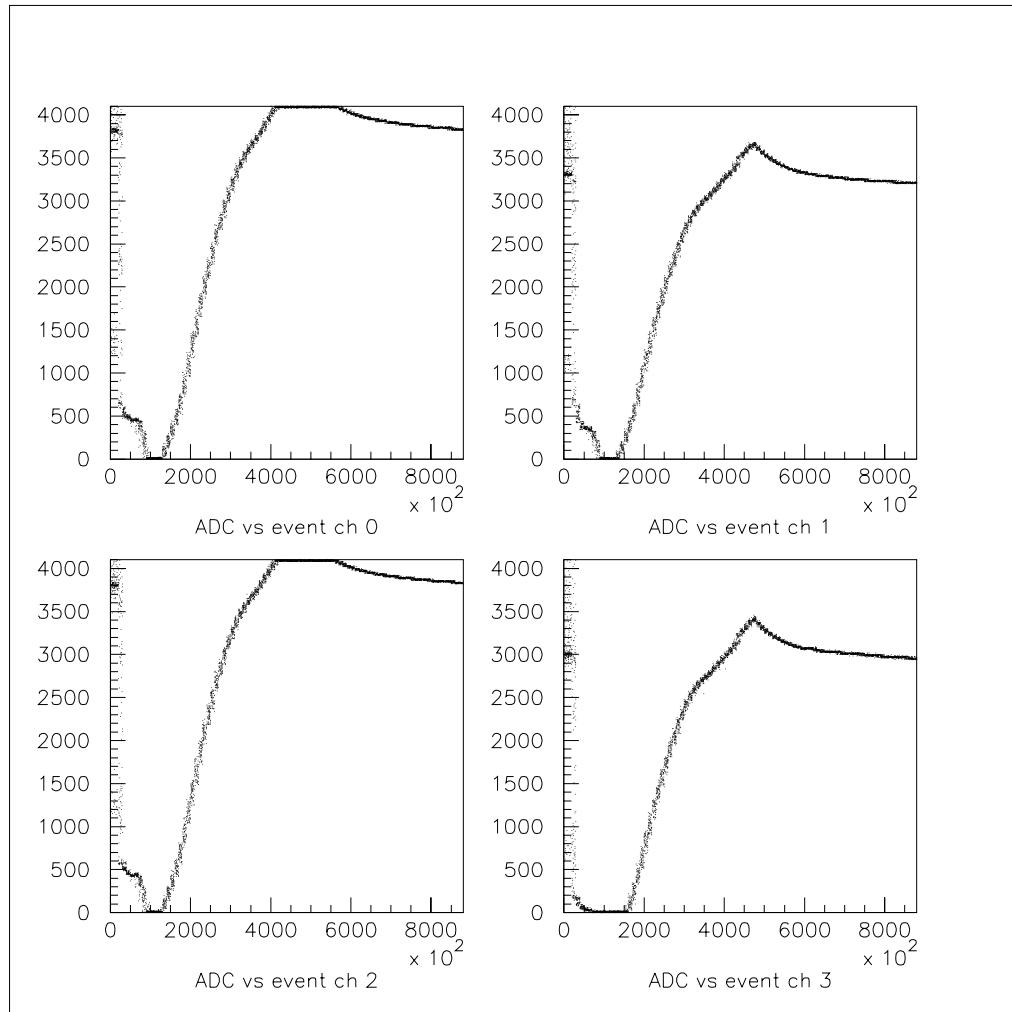

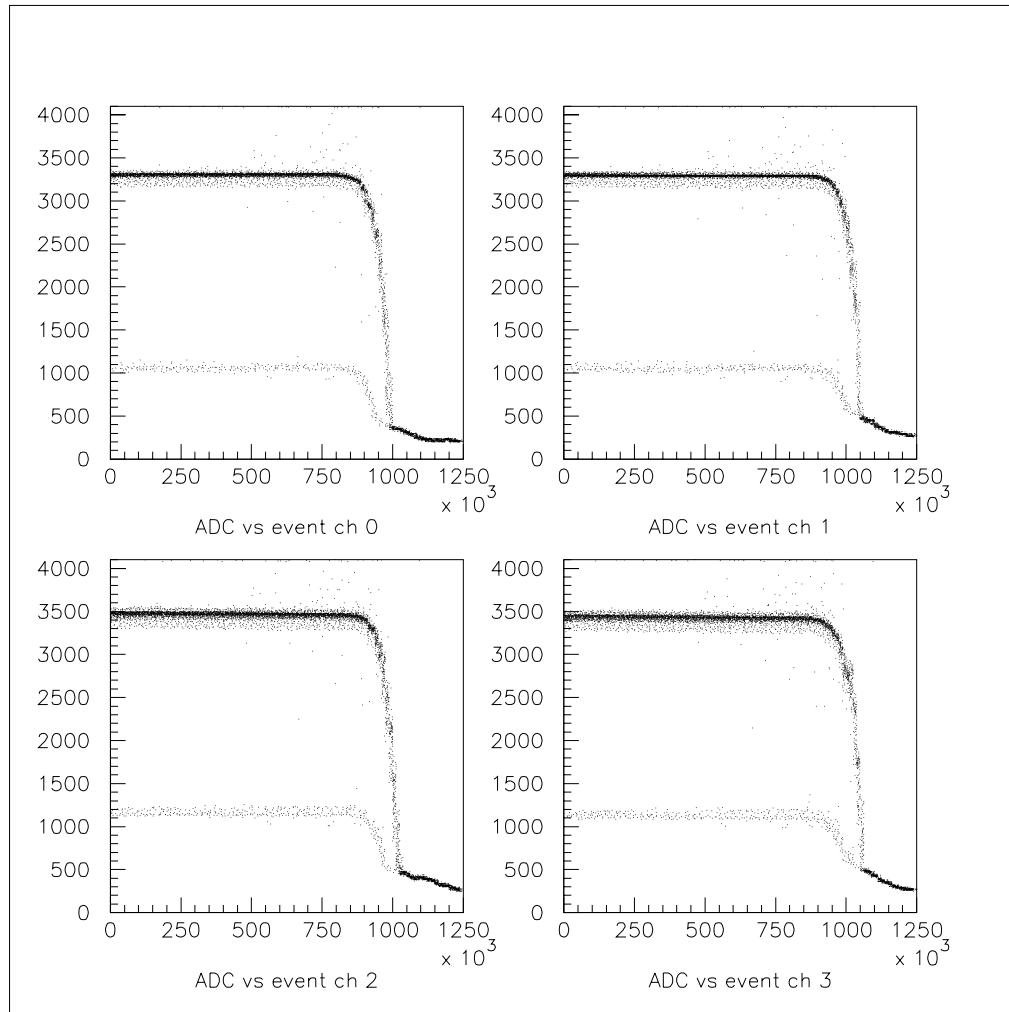

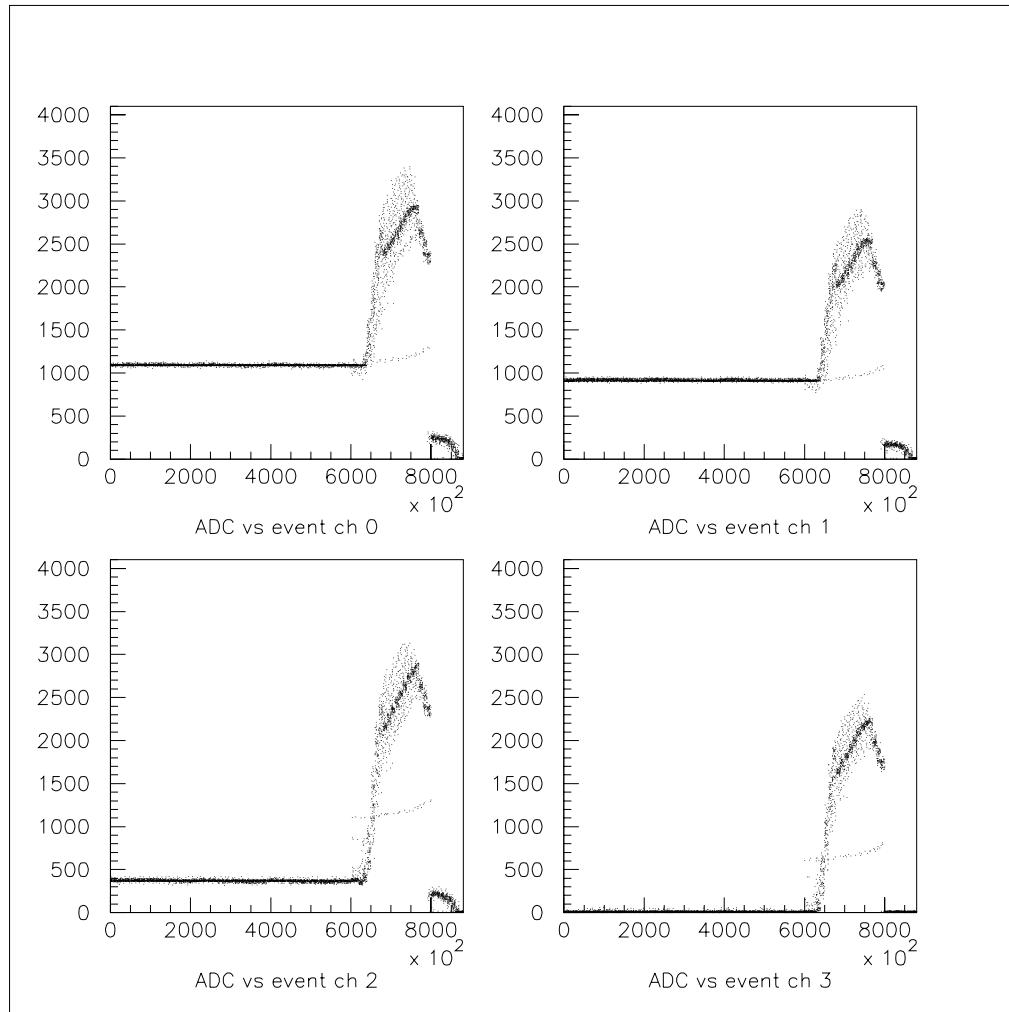

| 8.1 | Number of ADC counts versus event number (time) for the proton irradiation run, with voltage applied. . . . .                                     | 82 |

| 8.2 | Number of ADC counts versus event number (time) for the proton irradiation run, without voltage applied. . . . .                                  | 83 |

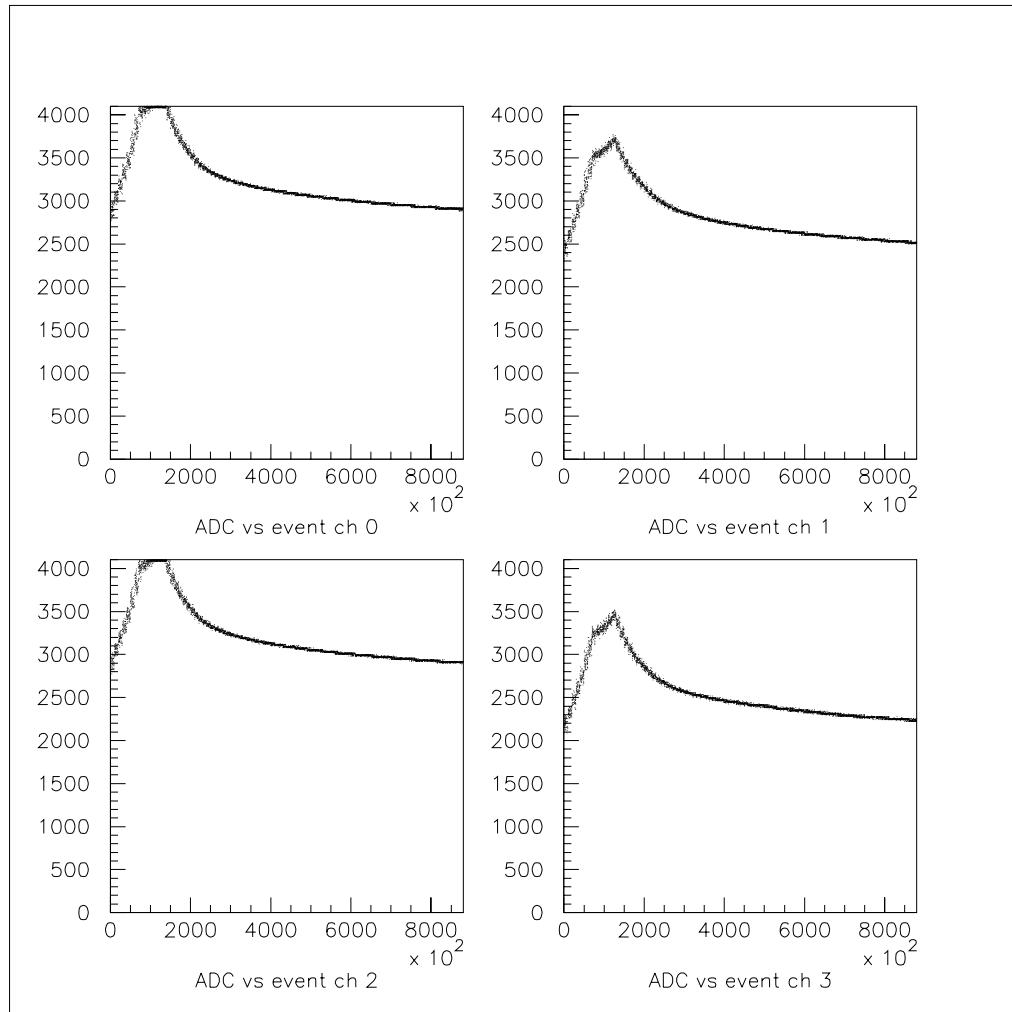

| 8.3 | Number of ADC counts versus event number (time) for the electron irradiation run, with voltage applied. . . . .                                   | 85 |

| 8.4 | Number of ADC counts versus event number (time) for a proton irradiation run in which the SCA chip, operated at pedestal voltage, died. . . . .   | 87 |

| 8.5 | Mean number of ADC counts versus time (minutes) for Chip A. . . . .                                                                               | 92 |

| 8.6 | RMS noise (ADC counts) versus time (minutes) for Chip A. . . . .                                                                                  | 94 |

|      |                                                                                                                                       |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.7  | Mean number of ADC counts versus time (minutes) for Chip B. . . . .                                                                   | 98  |

| 8.8  | RMS noise (ADC counts) versus time (minutes) for Chip B. . . . .                                                                      | 101 |

| 8.9  | Mean number of ADC counts versus time (minutes) for Chip C. . . . .                                                                   | 105 |

| 8.10 | RMS noise (ADC counts) versus time (minutes) for Chip C. . . . .                                                                      | 108 |

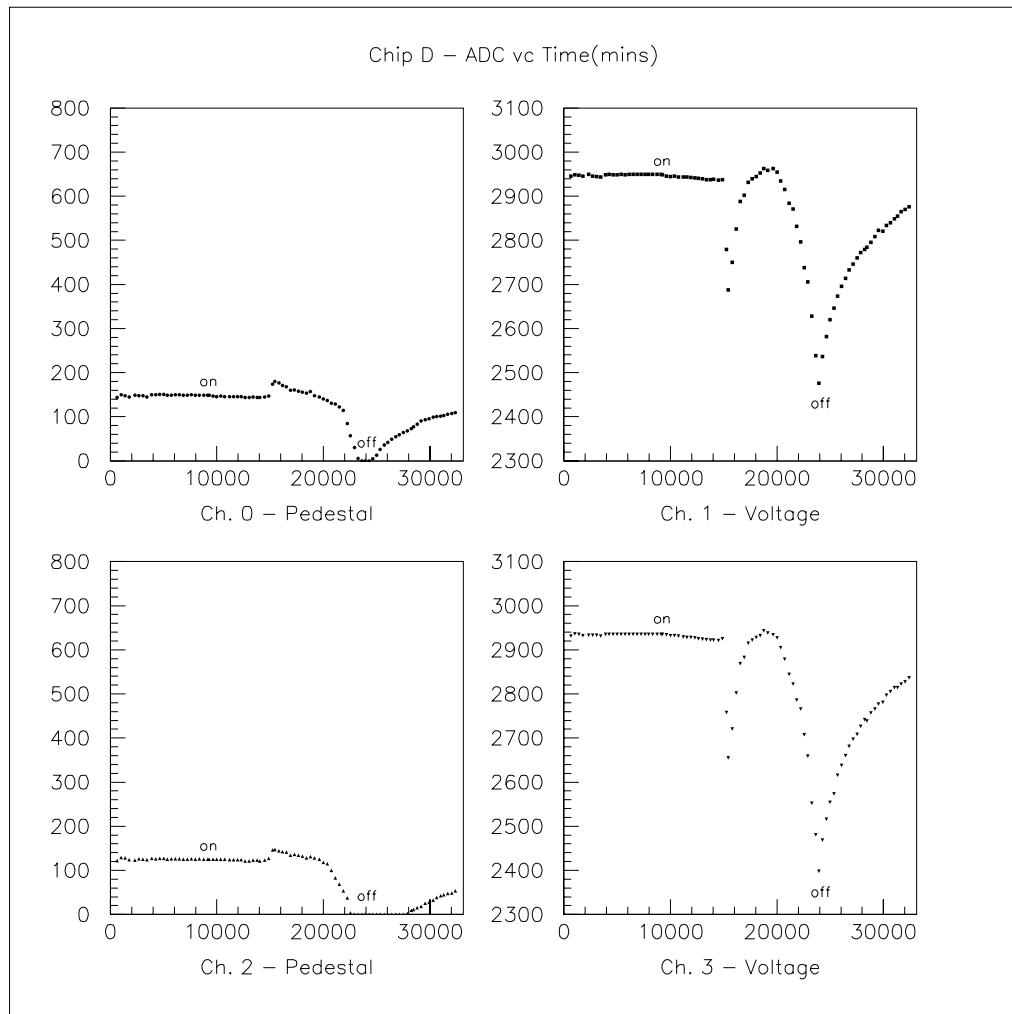

| 8.11 | Mean number of ADC counts versus time (minutes) for Chip D. . . . .                                                                   | 112 |

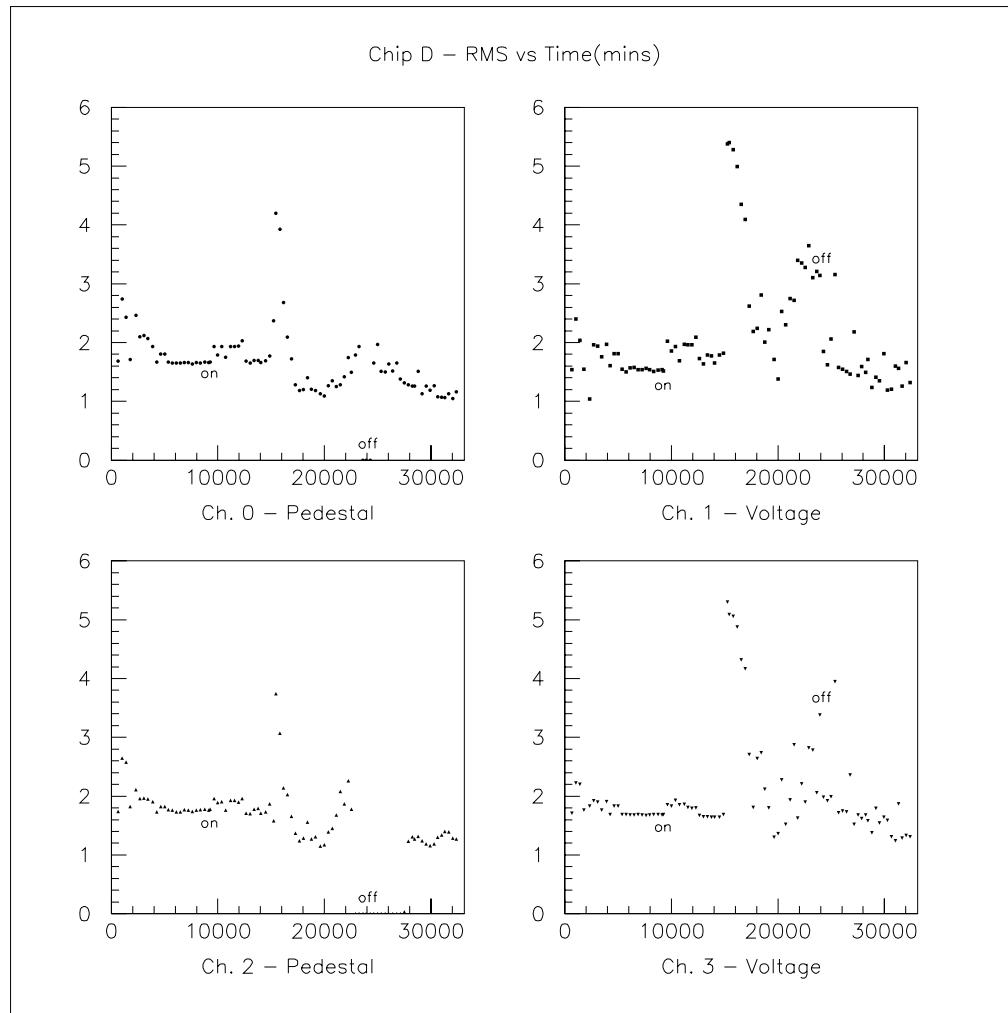

| 8.12 | RMS noise (ADC counts) versus time (minutes) for Chip D. . . . .                                                                      | 114 |

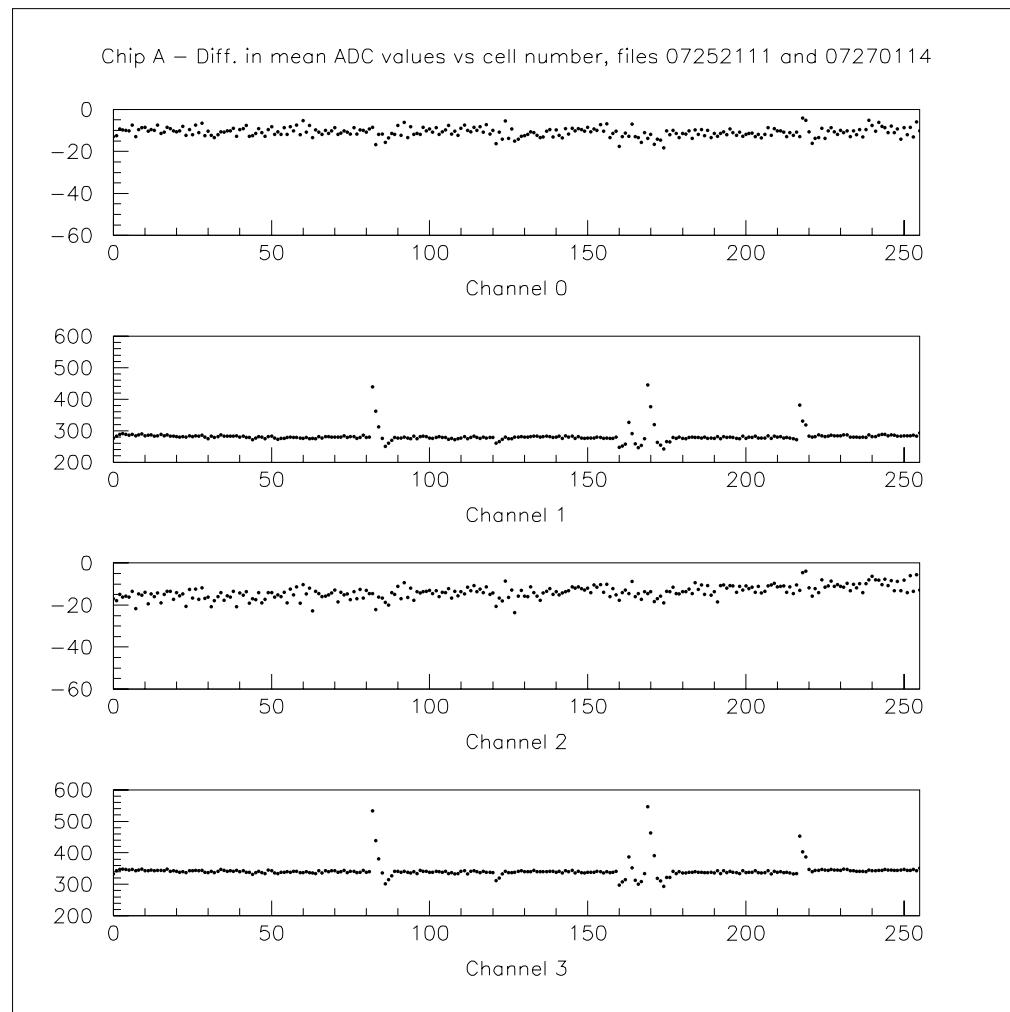

| 8.13 | Difference in mean ADC values versus cell number between files 07252111<br>and 07270114 for all four channels. . . . .                | 118 |

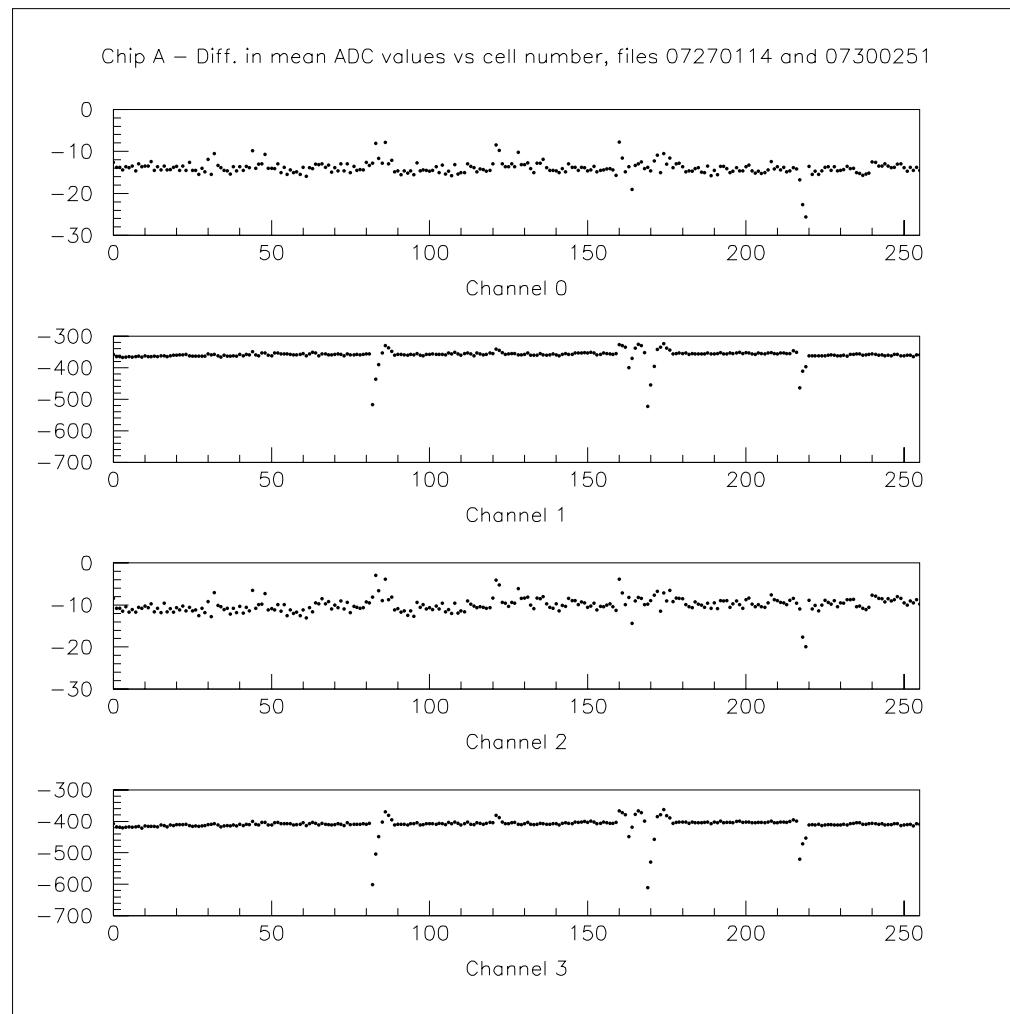

| 8.14 | Difference in mean ADC values versus cell number between files 07270114<br>and 07300251 for all four channels. . . . .                | 119 |

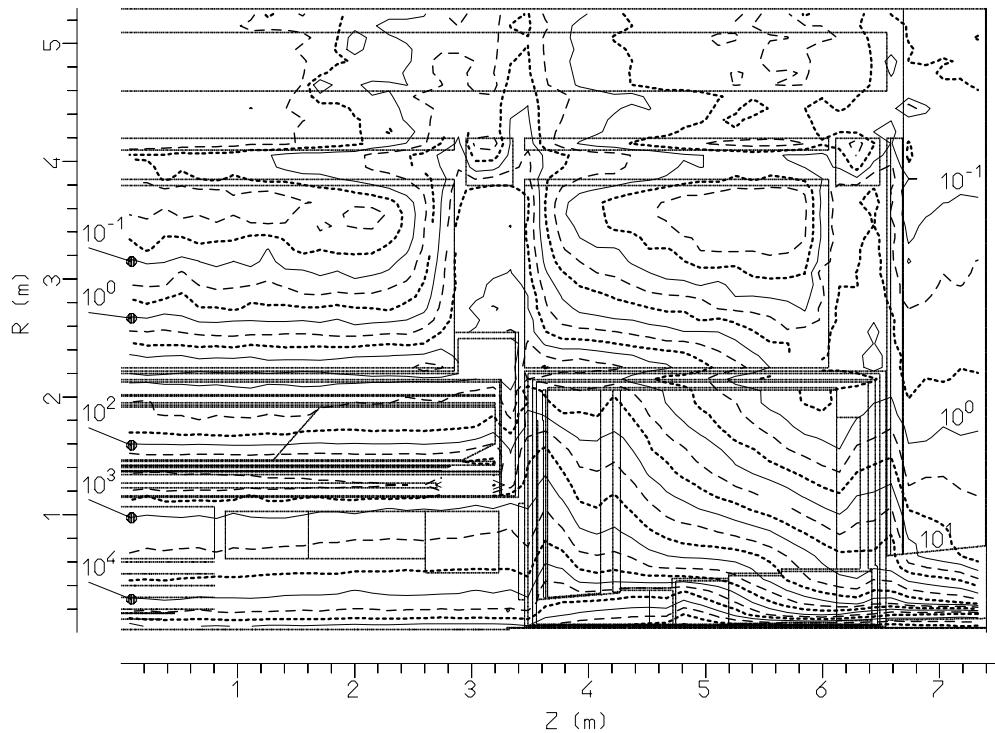

| 8.15 | Yearly integrated dose (Gy/yr) in the inner detector and the calorimeters<br>(taken from the ATLAS Technical Proposal, 1994). . . . . | 122 |

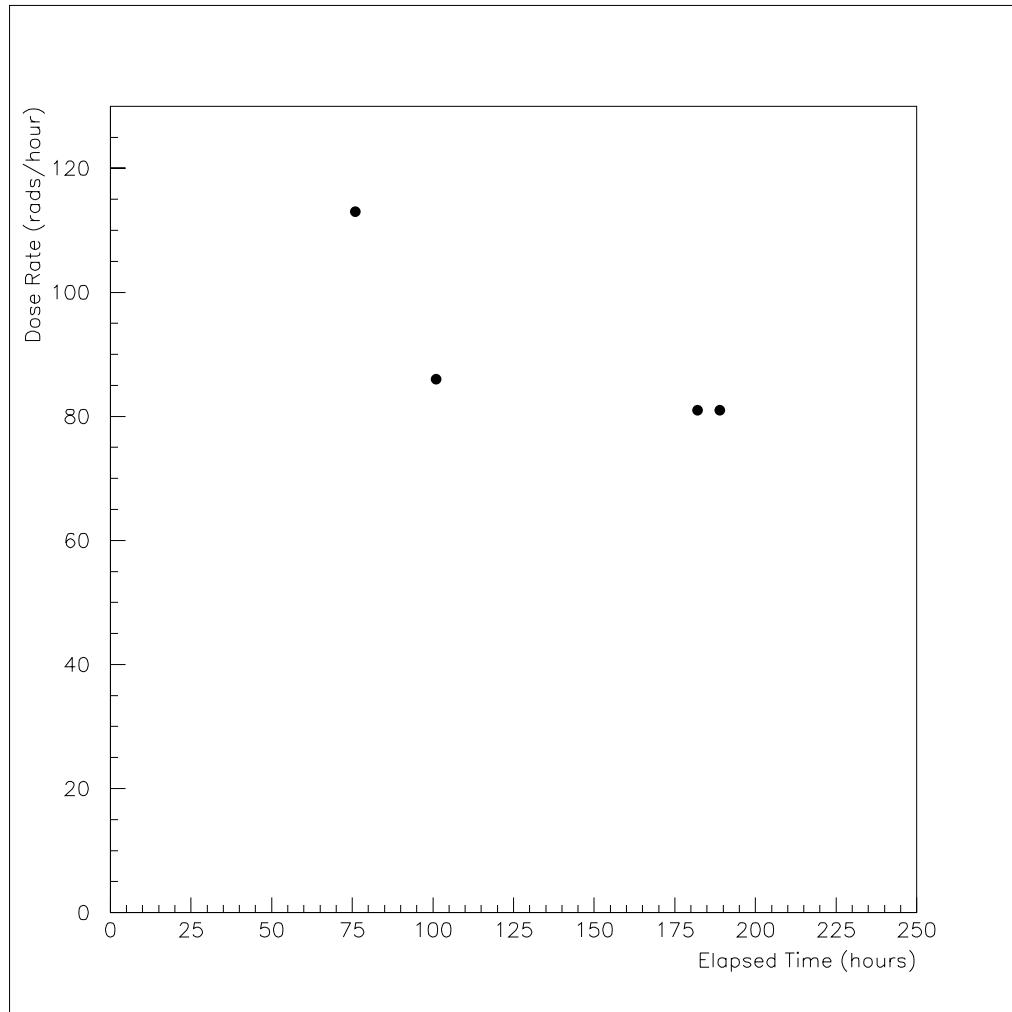

| 8.16 | Dose rate (rad/hour) versus elapsed time (hours) to point where effects<br>are observed, for gamma irradiation of SCA chips. . . . .  | 124 |

# CHAPTER 1

## Introduction

The Large Hadron Collider (LHC), to be built at CERN (the European Laboratory for Particle Physics), Geneva, will allow physicists to study particles and their interactions at energies in the TeV range. There will be numerous new physics opportunities, including the search for a Higgs boson. Of course, a very complicated tool will be needed to detect these particles and to determine their properties. The proposed ATLAS (A Toroidal LHC ApparatuS) detector is such a tool.

The ATLAS Collaboration currently consists of about 1500 physicists and engineers, from over 140 institutions. The numerous development tasks have been divided amongst the participating institutions.

Many of the processes that physicists hope to study with the ATLAS detector are very rare. To compensate for this, the LHC will operate at a very high collision rate. This puts serious demands on the performance of the detecting equipment of ATLAS, as well as on the readout electronics that will transmit signals from detector elements. In order to fully exploit the high rate of the LHC, new electronics systems have been developed. Because all detector signals are processed by electronics, it is very important to use the most efficient, reliable and accurate readout system that can be attained.

One method of dealing with the high rate of the LHC is through the use of a pipeline, whereby signals from the detector are temporarily stored until a preliminary

analysis has been performed. Then, the signals are either discarded, or further analyzed. One scheme of pipelining detector signals makes use of a switched capacitor array (SCA) chip, which contains capacitors that store the analog charge collected from cells of the detector.

This thesis presents the pipelining scheme based on SCA chips, and also documents several tests which have been performed on these chips. These tests may be divided into two areas. A number of tests were conducted to determine the electronic noise of the SCA chips, and to analyze the components of the noise. Also, SCA chips have been irradiated, in order to determine their tolerance and response to various types of radiation.

It will be shown that a pipeline system which makes use of SCA chips is a viable solution to the ATLAS fast-electronics requirements.

# CHAPTER 2

## Physics Motivation

The major physics issues which will be studied at the LHC include the search for the Higgs boson, top-quark physics, B-physics, and a search for supersymmetric particles. The ATLAS detector is designed to examine all of these topics. As a general-purpose detector, ATLAS also has the capability of exploring physics beyond that discussed in this chapter, which demonstrates its tremendous physics potential.

### 2.1 Higgs Search

The Standard Model (of fundamental particles and their interactions) unifies the electroweak force and the strong force. The most prominent physics opportunity at the LHC is the search for the origin of spontaneous symmetry-breaking in the electroweak sector of the Standard Model. The existence of a neutral Higgs boson ( $H$ ) is a possible manifestation of the spontaneous symmetry-breaking mechanism. One of the primary objectives of the ATLAS detector at the LHC is the discovery of the neutral Higgs boson and the subsequent investigation of its properties. Experimental searches for the Higgs boson present a major challenge to physicists. The mass of the Higgs boson is undetermined in the Standard Model, so one must be prepared to search over a mass range extending up to 1 TeV<sup>1</sup> and possibly beyond [1].

---

<sup>1</sup>By convention, mass units of  $eV/c^2$  (where  $c$  is the speed of light in a vacuum) are simplified to  $eV$ .

For heavy Higgs bosons,  $m_H > 2m_W$ , the dominant decays are  $H \rightarrow W^+W^-$  and  $H \rightarrow ZZ$  so that the best place to look for evidence of the heavy Higgs boson at hadron supercolliders is in  $pp \rightarrow VVX$  processes, where  $V = W^\pm, Z$  [3].

For  $180 < m_H < 800$  GeV, the most promising channel is the 4-lepton channel,  $H \rightarrow ZZ \rightarrow 4\ell^\pm, 2\ell^\pm 2\nu$  (which have branching ratios of 0.0014 and 0.0088, respectively), even though the rate is very limited at the high end of the mass range. Here, the Higgs width grows rapidly, as do the momenta of the leptons to be measured. Therefore, the observation of a possible Higgs signal in this channel depends more on the luminosity than on detector performance. Previous studies [2] showed that a Higgs boson with  $m_H \leq 800$  GeV should be detected in this channel for an integrated luminosity of  $10^5$  pb $^{-1}$ . For larger Higgs boson masses, the event rate is too small to observe a clear signal, and to extend the range of observability would require an increased data sample. At lower masses the signal rates are high, such that with an integrated luminosity of  $10^4$  pb $^{-1}$  a Higgs boson with mass between 200 and 300 GeV may be detected separately in the 4-muon and 4-electron channels.

On the other hand, the Higgs decay,  $H \rightarrow W^+W^- \rightarrow \ell\nu q\bar{q}$ , offers the possibility of exploiting the much larger branching ratio of about 0.20. In this case, however, there is a sizeable background from W multijet production where two of the QCD jets have an invariant mass close to  $m_W$  and fake the  $W \rightarrow q\bar{q}$  decay [3].

For Higgs masses larger than the reach accessible to the 4-charged-lepton channel, the  $H \rightarrow \ell\ell\nu\bar{\nu}$  channel may be considered. This channel benefits from a branching ratio which is at least six times greater, but the decay cannot be completely reconstructed because of the escaping neutrinos.

The decay  $H \rightarrow \gamma\gamma$  is a rare decay mode. It is only detectable in a limited Higgs mass region where the production cross-section and the decay branching ratio

are both relatively large. It is the most promising channel for a Higgs search in the mass range  $80 < m_H < 120$  GeV.

In order to search for the Higgs boson, the ATLAS detector must be able to probe many of these channels. This places considerable demand in terms of resolution on the detector elements, and on the readout electronics.

## 2.2 Top-Quark Physics

The rate of top-quark production at the LHC will be large, and will allow measurement of the top-quark mass in different channels. Even at the moderate luminosity expected during the first years of LHC operation (about  $10^{33}$  cm $^{-2}$ s $^{-1}$ ), roughly  $10^7$   $t\bar{t}$  pairs will be produced each year. The mass of the top-quark,  $m_t$ , may be measured by studying  $t\bar{t} \rightarrow (\ell\nu b)(jjb)$  decays.  $t \rightarrow jjb$  decays (where  $j$  represents a jet) will provide an abundant event sample, and will allow direct reconstruction of  $m_t$ , through the invariant mass of the 3-jet system. A high- $p_T$  (transverse<sup>2</sup> momentum) lepton from the other top-quark decay will provide the trigger, which means that the lepton will be used to identify the decay. A few difficulties which must be handled are: background from other processes (such as fake electrons + jets,  $b\bar{b}$  + jets, and  $W +$  jets), combinatorial background from the jets in  $t\bar{t}$  events, and systematic uncertainties due to the detector and the theoretical models used [4, 5].

Despite the large signal rate, background from other processes must be considered. If the  $t\bar{t}$  events are triggered on electrons, jets which fake the electron signature will cause a large background. To reduce multijet backgrounds well below the high- $p_T$  electron signal, a rejection against jets of about  $10^5$  is necessary. The background

---

<sup>2</sup>Perpendicular to the beam axis.

from  $b\bar{b} + \text{jets}$  can be reduced well below the  $t\bar{t}$  signal using lepton isolation and missing transverse energy. The background from  $W + \text{jets}$  is of the same order of magnitude as the signal, and can only be reduced by requiring that at least one reconstructed high- $p_T$  jet be tagged as a b-jet [6].

A signal-to-background ratio greater than one may be obtained by requiring that three jets with  $p_T > 40$  GeV and  $|\eta|^3 < 2$  be reconstructed in the hemisphere opposite to the trigger lepton, that one of them be tagged as a b-jet and that the remaining pair have an invariant mass consistent with  $m_W$ .

Another way in which  $m_t$  may be accurately measured is through the use of multileptonic events from top-quark decays. Two leptons from the same top-quark decay would be used [7]. A third high- $p_T$  lepton is required to minimize the background contribution. Thus, two leptons from  $W$  decay and one lepton from b-quark decay will form the signal sample for the mass measurement.

Searches for rare top-quark decays such as  $t \rightarrow bH^+$  and  $t \rightarrow Zc$  will also be performed. The decay  $t \rightarrow bH^+$ , if kinematically allowed, can compete with the  $t \rightarrow bW$  decay, according to extensions of the Standard Model which include charged Higgs bosons [6]. The  $H^+$  decays either to  $\tau\nu_\tau$  or  $c\bar{s}$ . By requiring at least one isolated high- $p_T$  lepton within  $|\eta| < 2.5$ , a large number of  $t\bar{t}$  events may be obtained. The main background processes are  $b\bar{b}$ ,  $W + \text{jets}$ , and combinatoric background from real and fake  $\tau$  in  $t\bar{t}$  events. The  $b\bar{b}$  background will be reduced by imposing additional isolation cuts. The other contributions to the background will be reduced by requiring at least three reconstructed jets with  $p_T > 20$  GeV and  $|\eta| < 2.5$ . Two of these jets will be tagged as b-jets.

---

<sup>3</sup>The pseudorapidity  $\eta$  is defined by  $\eta = -\ln(\tan \frac{\theta}{2})$ , where  $\theta$  is the polar angle (the angle with respect to the beam axis).

Applying these selection cuts to  $t \rightarrow bH^+$  decays would result in final states where an excess of events with one isolated  $\tau$  (compared to events with an additional lepton) would be observed. It is expected that the signal from  $H^+$  can be observed for  $m_{H^+} < 130$  GeV.

Another rare decay of the top-quark,  $t \rightarrow Zc$  (where  $c$  represents a charm quark), is expected to occur at a negligibly small rate in the Standard Model. This decay, if it is observed, would thus provide a glimpse of physics beyond the Standard Model. Also, this decay is of interest because a major source of background to events containing  $Z$ -boson pairs and jets is the decay  $t\bar{t} \rightarrow ZZ + CC$ <sup>4</sup>. For  $t\bar{t} \rightarrow ZcWb$  with subsequent decays  $Z \rightarrow \ell\ell$  and  $W \rightarrow jj$ , the signal would be identified as events with a reconstructed  $Z \rightarrow \ell\ell$  decay accompanied by at least three jets with  $p_T > 50$  GeV, one of which is tagged as a  $b$ -jet, and with one  $Z +$  jet combination of invariant mass within  $\pm 8$  GeV of  $m_t$  [6].

## 2.3 B-Physics

B-physics is a rich field, and the very large cross-section for  $b$ -quark production at the LHC will allow for a wide range of precision measurements. These include a study of CP violation<sup>5</sup> through the decays  $B_d^0 \rightarrow J/\psi K_s^0$ ,  $B_d^0 \rightarrow \pi^+\pi^-$ , and  $B_s^0 \rightarrow J/\psi \phi$ . Also, a search for rare  $b$  decays such as  $B_d^0 \rightarrow \mu^+\mu^-$  and  $B_s^0 \rightarrow \mu^+\mu^-$  will be performed. Another interesting possibility is the measurement of  $B_s^0$  mixing.

Much of the B-physics program will be performed during the first few years of LHC operation. B-physics studies will be experimentally easiest at the initial

---

<sup>4</sup>Charge conjugate.

<sup>5</sup>CP conservation implies that the behavior of particles is unchanged under simultaneous charge (C) and parity (P) transformations. Violations of CP conservation have been observed.

luminosity of about  $10^{33}$  cm $^{-2}$ s $^{-1}$ , because pile-up<sup>6</sup> effects will be small, and the vertex detectors very close to the beam pipe will not yet be damaged by radiation.

The ATLAS detector is well-suited to perform a B-physics study, because of its powerful and flexible trigger system, high-resolution secondary-vertex measurement, and efficient track reconstruction and electron measurement down to low  $p_T$  [6]. The first level of triggering for B-physics requires a muon with a  $p_T$  threshold of 6 GeV and with  $|\eta| < 2.2$ . The second-level trigger reduces the rate by making a sharper  $p_T$  cut on the muon using the precision muon detectors and the inner tracking. Muons with  $p_T \geq 5$  GeV and  $|\eta| < 2.5$  can be identified in the external muon system. The vertex detector is capable of measuring B-decay vertices with a resolution of approximately 50  $\mu$ m.

## 2.4 Supersymmetric Particles

Supersymmetric extensions of the Standard Model predict a large number of new particles, with masses and production rates such that the LHC is suitable for searching for these particles. The ATLAS detector would be able to discover such particles over a large fraction of the parameter space. It is expected that ATLAS will play a crucial role in either revealing or excluding supersymmetric extensions to the Standard Model.

In the framework of the minimal supersymmetric extension to the Standard Model, many possible signatures have been proposed for detecting supersymmetric particles. Some are very clean signals, but are significant in only a small region of

---

<sup>6</sup>Pile-up occurs when the signals from particles from different interactions overlap in the detector.

the available parameter space [8]. Three main signatures which would allow the exploration of a large fraction of the parameter space have been identified, namely multijets and missing transverse energy searches from squark/gluino production, same-sign dilepton searches from squark/gluino production, and three-lepton events from chargino/neutralino production [6]. Also, signatures in which a Higgs boson is present in the decays of squarks and gluinos have been studied [10].

## 2.5 Summary

The high energy and large collision rate of the LHC will provide a large number of physics opportunities. The ATLAS detector is designed to fully exploit the discovery potential afforded by the LHC. Thus, it must be able to explore all of the above physics issues with high precision. The precision with which results are obtained is arguably the most important design consideration of any detector. The readout electronics which process the signals from the various detector components must also operate with very high precision. The large collision rate and high energy of the LHC place challenging requirements on the readout electronics, and this thesis is concerned with a readout system which meets this challenge.

# CHAPTER 3

## The Large Hadron Collider

The Large Hadron Collider is a proton-proton collider, which will be installed in the existing 27 km circular LEP (Large Electron Positron) tunnel at CERN. It is expected that the center of mass energy of LHC collisions will be 14 TeV. Such a high energy is unprecedented in the world of particle colliders, and will undoubtedly provide a large number of physics opportunities.

The LEP collider is able to simultaneously accelerate electrons and positrons in opposite directions, using the same magnets. If the LHC were a proton-antiproton collider, it could employ a similar magnet system. However, it is very difficult to produce antiprotons, so this option is not viable. In order to collide two beams of protons, it is necessary to accelerate them in separate magnetic channels. To accomplish this, the LHC magnets will be twin bore magnets which have two separate beam channels within the same mechanical structure and cryostat. The superconducting dipole magnets will provide a magnetic field of 8.4 T.

There will be eight interaction points around the LHC ring. At each interaction point, the two beams of protons, which are circulating in opposite directions, will cross. Large, general purpose detectors (ATLAS and CMS (Compact Muon Solenoid)) will be placed at two of these interaction points.

Many of the physics processes that will be studied are very rare events. In order to obtain significant quantities of data of such events, a very large number

of total events must take place. Thus, it may be a problem to perform conclusive experiments in a reasonable amount of time. This dilemma will be avoided by having a large number of collisions per unit time. The design rate of proton bunch-crossings at the LHC is 40 MHz. Another characteristic of the LHC is a high luminosity, which is the number of particles per unit area per unit time. The design LHC luminosity is about  $10^{34} \text{ cm}^{-2}\text{s}^{-1}$ , although the initial luminosity will be lower.

# CHAPTER 4

## The ATLAS Detector

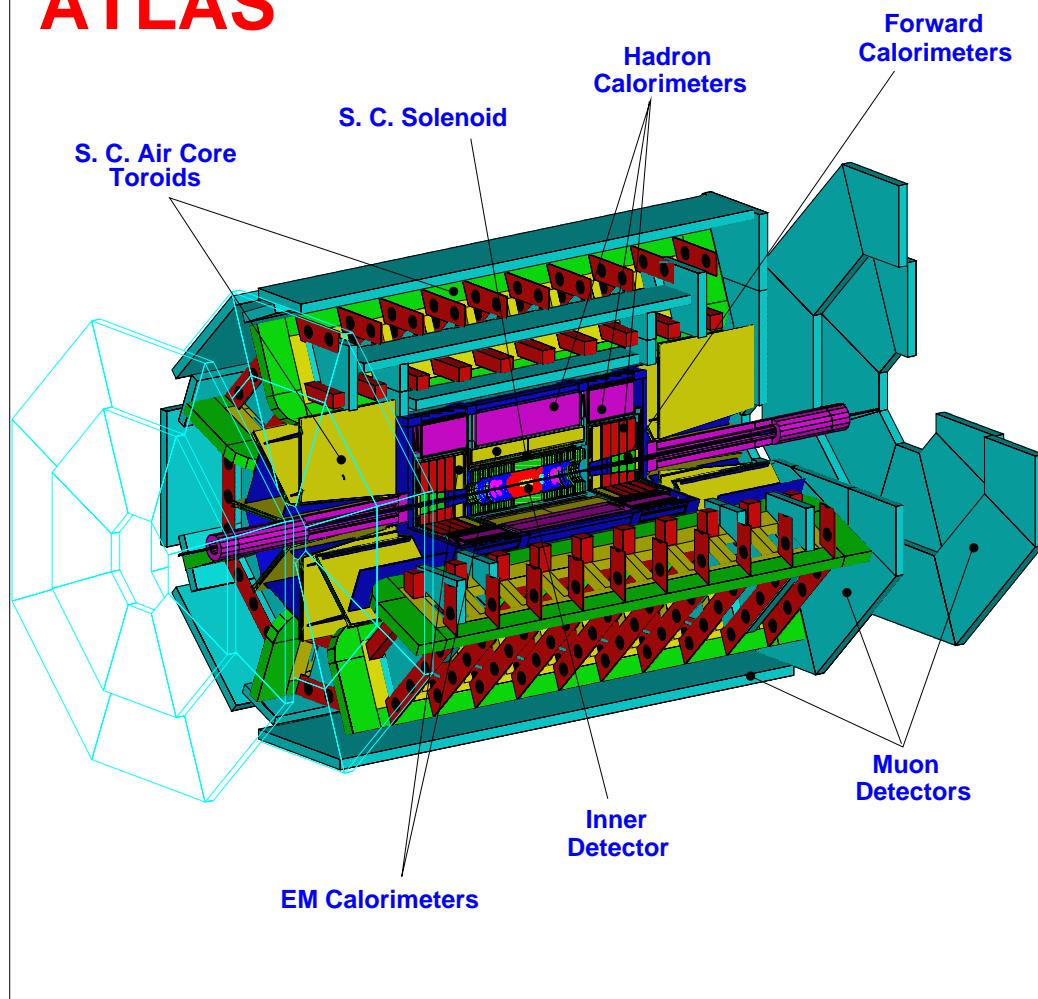

The ATLAS [6] detector is a proposed general purpose detector for the Large Hadron Collider, capable of exploring the new energy regime which will become accessible. The ATLAS detector would be fully operational at the startup of the new accelerator, and is designed to study a wide range of physics issues, such as top quark decays, B-physics, supersymmetry searches, and Higgs boson searches. The detector's versatility also demonstrates a potential to cope with unexpected new physics [9]. An isometric view of the ATLAS detector is shown in Figure 4.1.

The ATLAS detector is designed to fully exploit the discovery potential of the LHC. Thus, the ATLAS detector must be able to operate efficiently at the LHC beam-crossing rate of 40 MHz, and at the LHC luminosity of  $10^{34} \text{ cm}^{-2}\text{s}^{-1}$ .

It is important for any experiment to accurately identify particles and measure their energies. The ATLAS detector will provide signatures of electrons, muons and jets, as well as making high precision momentum measurements of charged particles. The magnet configuration is a crucial element that dictates the precision of the detector. An air-core muon magnet system and an inner superconducting solenoid will be used.

The ATLAS design consists of three main components: an inner detector, calorimetry, and muon detectors. The inner detector will perform tracking; the calorimetry will measure the energies of electrons, photons and hadronic jets; and the

# ATLAS

Figure 4.1: The ATLAS detector.

muon system will identify and make accurate momentum measurements of muons.

## 4.1 The Inner Detector

The principle aims of the central tracking system are to contribute to the detection and identification of leptons, photons (which have converted to electron-positron pairs) and hadrons over a large rapidity range, to measure high- $p_T$  charged tracks, and to provide information for the second level of triggering [11].

The main requirements for high-luminosity operation include tracking coverage over the pseudorapidity range  $|\eta| < 2.5$ , tracking efficiencies of greater than 90%, electron-finding efficiencies of greater than 90%, tagging of b jets with a greater than 30% efficiency, and measurement of the z coordinate of primary vertices with at least four charged tracks to better than 1 mm [12].

The inner detector is very important for B-physics studies, because it provides a powerful and flexible trigger system, high-resolution secondary vertex measurement, and efficient track reconstruction and electron identification down to low  $p_T$ . As mentioned previously, B-physics studies will be easiest during initial lower-luminosity operation, because the pile-up effects would be small, and vertex detectors placed close to the beam pipe could survive for several years, before radiation damage occurs.

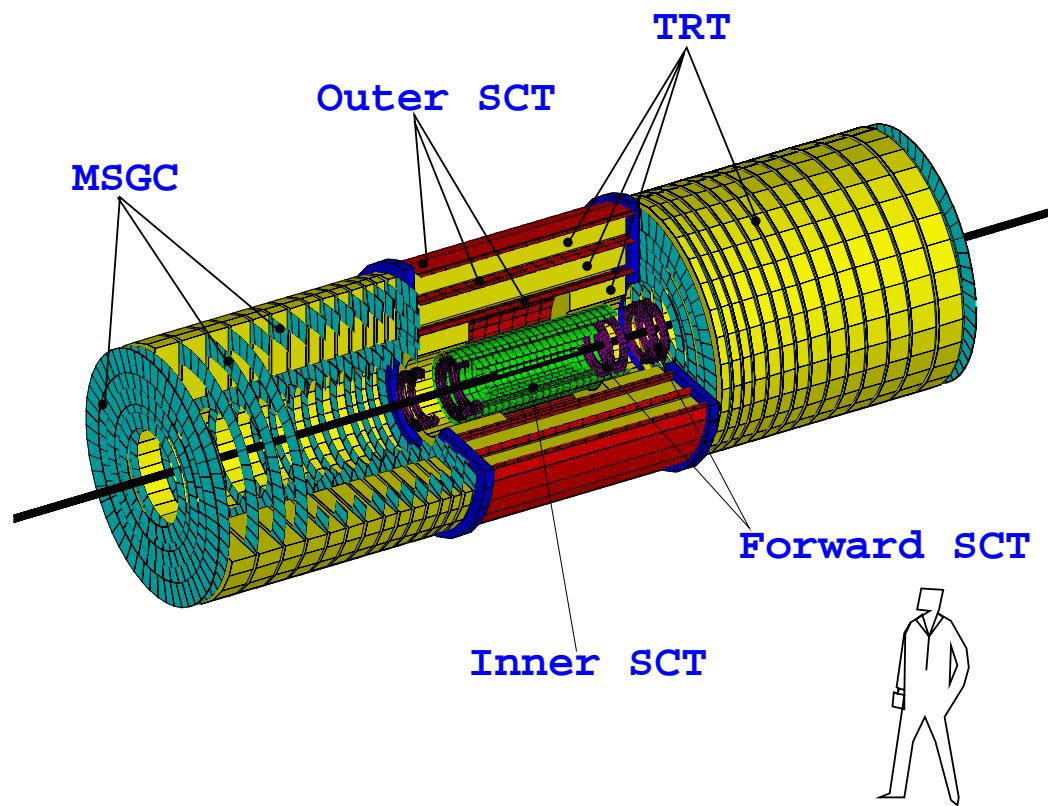

The inner detector consists of a barrel section between polar angles of  $45^\circ$  and  $135^\circ$ , and a forward section on each end. In the barrel region, the detectors are concentric cylinders, parallel to the beam axis, and in the forward part, they are “wheels” transverse to the beam axis. These geometries are intended to reduce the path length of particles through the material.

The general concept of the inner detector is to use a combination of a few

high-precision layers in the inner part of the tracker, and straw tubes in the outer part which supply a large number of measurements on the track trajectories [6]. This concept offers the benefits to pattern recognition of a device which makes a large number of “continuous” track measurements over a long track length, as well as those of a smaller number of higher-precision discrete points. In the barrel region, straw tubes provide continuous tracking, and semiconductor technology is used for discrete tracking. The semiconductor tracker (SCT) [13] consists of pixel detectors near the beam pipe, and silicon and GaAs strip detectors. In the forward regions, radial straw tubes are used for continuous tracking, and radial microstrip gas counters (MSGC) [14] provide discrete tracking. In order to measure and identify primary and secondary vertices, a semiconductor detector is placed close to the interaction point. Radiator material will be placed around the straw tubes and will detect transition radiation. Such a Transition Radiation Tracker (TRT) will assist in the identification of electrons.

Figure 4.2 shows the layout of the Inner Detector. It will fit inside the cryostat of the barrel electromagnetic calorimeter. A superconducting solenoid, integrated into the cryostat of the electromagnetic calorimeter, will provide a magnetic field of 2 T along the beam axis.

The choice of semiconductor technology in the barrel region of the inner tracker is determined by the location and intended function [6]. The outer detector layers (at radii of about 50 cm) have a large area and are made out of single-sided silicon microstrip detectors to reduce cost. The detector layers at radii of 20 and 30 centimeters are close to the vertex, and so should consist of a small amount of material to minimize bremsstrahlung effects. This can be achieved by using double-sided silicon microstrip detectors. The innermost detector layers, at radii of 11.5 and 14.5 centimeters, are composed of silicon pixel detectors which provide point information

# ATLAS Inner detector

Figure 4.2: Three-dimensional cutaway view of the ATLAS Inner Detector (taken from the ATLAS Technical Proposal, 1994).

close to the vertex.

The design of the Inner Detector is influenced by physics requirements, environmental constraints, and overall cost. The Inner Detector Collaboration has concluded that the best compromise between these requirements is to use three technologies: semiconductors, microstrip gas counters, and a straw tracker with transition radiation enhancement.

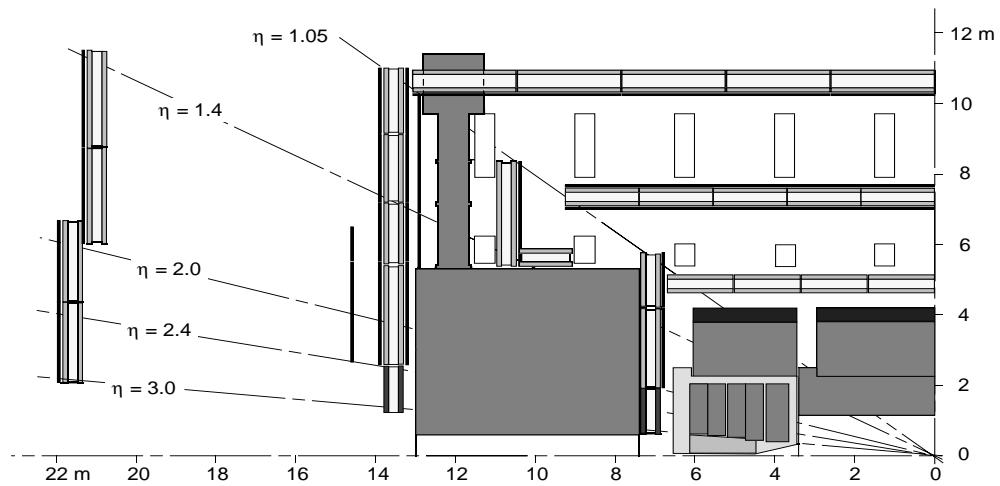

## 4.2 Calorimetry

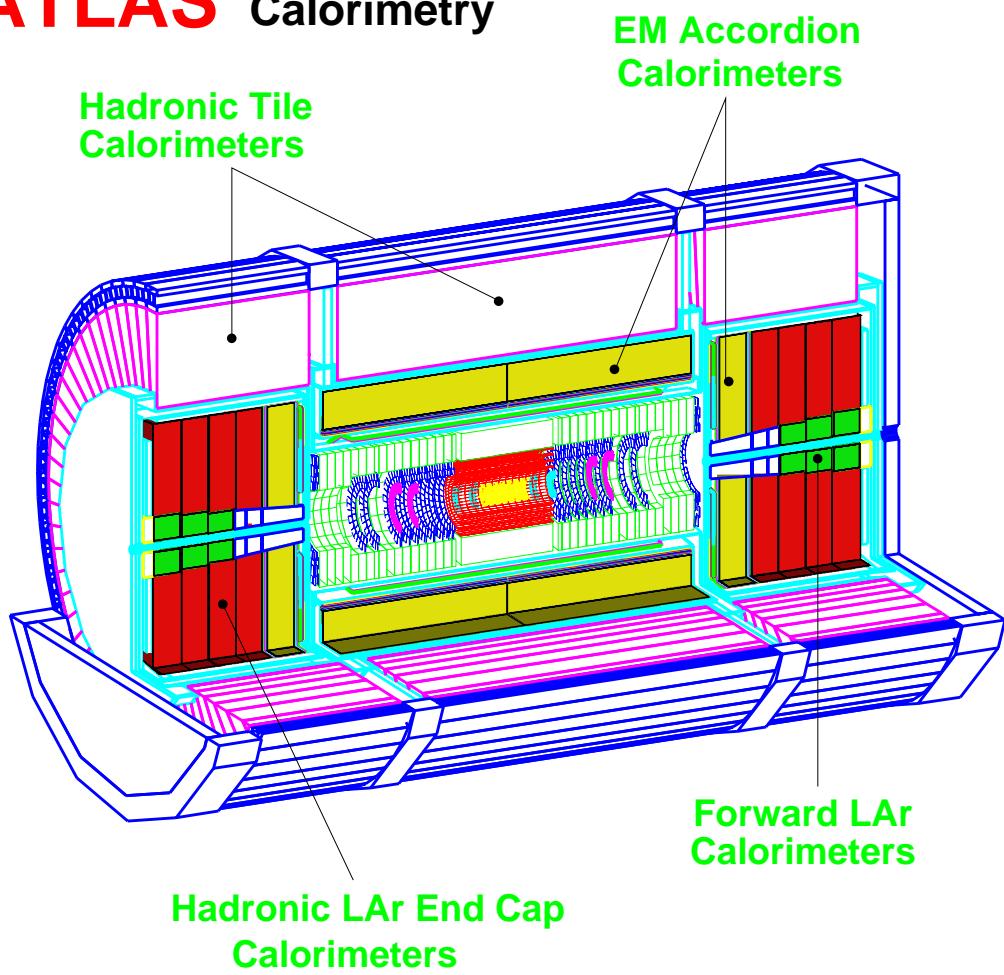

Calorimeters will be one of the most essential components of the detectors at the LHC. The main purpose of a calorimeter is to measure the energy and position of the particles which pass through it. This is done by sampling the energy deposited by the showers in the calorimeter. Some of the goals of ATLAS calorimetry are: efficient identification of photons and electrons in the energy range from 10 GeV up to a few TeV, hermetic jet and missing energy determination, effective triggering, and the ability to withstand the radiation level of the LHC [6]. A three-dimensional view of the ATLAS calorimeter system is shown in Figure 4.3.

The calorimetry consists of two types: lead/liquid argon (LAr) electromagnetic (EM) calorimetry, and hadronic calorimetry. The main calorimeter system covers  $|\eta| < 3.2$ . The calorimeter system can be divided into three parts, both geometrically and mechanically: a barrel part and two end-cap parts, one on each end of the barrel. The barrel and end-cap sections both consist of LAr EM calorimeters, followed by hadronic calorimetry which is thick enough to fully contain the very high energy jets produced by the LHC. The EM calorimeters will detect electrons, positrons and photons. The hadronic calorimeters will detect hadrons which pass through the EM

# ATLAS Calorimetry

Figure 4.3: Three-dimensional view of the ATLAS calorimeter system (taken from the ATLAS Technical Proposal, 1994).

calorimeters. Neutrinos will not be detected by the calorimetry.

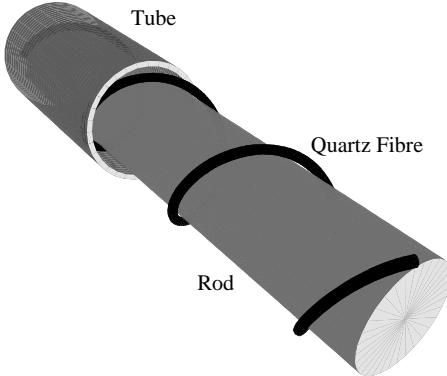

Calorimeters are also used to determine if there is missing transverse energy, which would signify the presence of undetected particles, such as neutrinos. Thus, full coverage is important, and so the calorimetry must extend to very small angles from the beam direction. To accomplish this, in the region  $3.1 < |\eta| < 4.9$ , forward calorimeters [15, 16] (both EM and hadronic) will be used. Because they must be placed very close to the beamline, the forward calorimeters must be significantly more radiation hard than the other calorimeters. This requires that a denser calorimeter be used. The forward calorimeter design consists of rods and tubes within an absorber matrix. Each rod is supported inside a tube by means of a quartz fibre, as shown in Figure 4.4, to form an electrode. The tubes are made of stainless steel. Liquid argon will fill the narrow gap between the inner diameter of the tube and the outer diameter of the rod. These electrodes will be placed in a hexagonal pattern within an absorber, with the electrode axes parallel to the beam line. Each of the forward calorimeters consists of three modules: an EM module, followed by two hadronic modules. The EM module will be made of copper, while for the two hadronic modules, the rods and matrix will be made of a tungsten alloy. The forward calorimeters will be integrated into the end-cap calorimeters, at a distance of about 5 meters from the interaction point.

In front of the barrel EM calorimeter will be placed the superconducting solenoid, which is designed to provide an axial magnetic field of 2 T at the center of the calorimetry. In order to minimize the amount of material present, the coil is designed to be as thin as possible, and also the vacuum vessels of the solenoid and barrel calorimeter will be combined.

There are three independent cryostats: a barrel cryostat and two end-cap

Figure 4.4: Exploded view of the tube electrode structure of the forward calorimeter (taken from the ATLAS Technical Proposal, 1994).

cryostats. The barrel cryostat contains the barrel EM calorimeter and the solenoid. Each end-cap cryostat contains the EM and hadronic end-cap calorimeters as well as the forward calorimeter. Each cryostat consists of two aluminum alloy vessels. The inner vessel is called the cold vessel and maintains the liquid argon at a temperature of 89 K. The outer vessel is called the warm or vacuum vessel and isolates the cold vessel from the outside. Superinsulation will be placed between the two vessels.

#### 4.2.1 Electromagnetic Calorimetry

The liquid argon technology was chosen for the EM calorimeter because it is radiation hard, and allows easy segmentation of the calorimeter into small cells, thus reducing pile-up. Argon has very good charge transport properties, however a drawback is the necessity of cryogenics. The RD3 Collaboration has made significant progress in designing and testing LAr EM calorimetry, based on the accordion concept [17].

In order to facilitate the efficient reconstruction and identification of electrons and photons, a LAr pre-shower detector was to be placed between the EM calorimeter

and the cryostat coil assembly, in both the barrel and end-cap regions. However, a cheaper and simpler approach will be employed, in which the first sampling of the EM calorimeter is segmented into very thin strips, and so may serve as a pre-shower device. The simplest arrangement has the strips narrow in  $\eta$ , providing a one-dimensional measurement.

The LAr EM calorimeters consist of plates of lead separated by liquid argon. A potential difference will exist across the LAr gaps. A charged particle passing through the liquid argon will ionize it, freeing electrons. These electrons will then drift towards the positively charged side of the LAr gap. This will produce a current, which can be amplified and measured. In reality, as say an electron passes through a calorimeter, it will shower. This will result in a large number of ionized tracks in the calorimeter. The total of all of the measured currents will be proportional to the total energy of the incoming particle. The LAr EM calorimeters will also detect photons, because as photons pass through the calorimeters, they will free electrons, which will then shower. The geometry of the LAr EM calorimeters is based on the accordion concept, and is shown in Figure 4.5.

Because lead is much denser than liquid argon, most of the incident particle's energy will be deposited in the lead plates. The lead is necessary to prevent any of the energy from escaping from the calorimeter and hence avoiding detection and measurement. But because of this, only a small amount of the incoming energy will actually be deposited in the liquid argon, and subsequently measured by the calorimeter. Thus, the LAr EM calorimeters only sample the energy of the shower periodically (in depth). By using many sections of liquid argon, one can obtain a high sampling frequency. Although such a calorimeter may only measure a small amount of the total energy deposited (typically about 10%), once the calorimeter has been calibrated, one can determine the total incoming energy.

Figure 4.5: Artist's view of an accordion calorimeter.

The energy resolution of electromagnetic calorimeters can be expressed as the quadratic sum of three terms:  $\frac{\Delta E}{E} = a\% \oplus \frac{b\%}{\sqrt{E}} \oplus \frac{c\%}{E}$ . The first term is the constant term, which does not vary with energy. It effects the energy resolution most at high energies, and is due to imperfections (such as non-uniformity) in the calorimeter construction and in the purity of the liquid argon. The second term is called the sampling term, and is inversely proportional to the square root of the energy. Thus, as the energy increases, the contribution from this term decreases. The sampling term can be reduced by increasing the sampling frequency. The third term in the energy resolution is due to electronic noise and pile-up, and is inversely proportional to the energy. Again, an increase in energy will reduce the contribution from this term. This third term is the one which is of concern to this thesis, and should be lower than the other terms over most of the energy range. It is expected that a constant term of less than 1% and a sampling term of less than or equal to  $10\%/\sqrt{E}$  would satisfy the goals of the ATLAS EM calorimetry.

Thus, we can see an important characteristic of both electromagnetic and hadronic calorimeters - the energy resolution improves as the energy increases.

#### 4.2.2 Hadronic Calorimetry

The primary purposes of the hadronic calorimetry in ATLAS are to identify jets and measure their energy, and to determine missing transverse energy [6]. Hadronic showers are detected with a poorer resolution than for EM calorimeters, partly due to the fluctuations in the amount of energy lost to nuclear binding energy effects. The energy resolution of a hadronic calorimeter is given by three terms, added in quadrature:  $\frac{\Delta E}{E} = \frac{a\%}{\sqrt{E}} \oplus b\% \oplus \frac{c\%}{E}$ . The first term is called the sampling term, and is due to the geometry of the calorimeter. The sampling term is proportional to

the inverse of the square root of energy. The second term is a constant term, which is due to imperfections in the construction and materials of the calorimeter, and also will have a contribution from an unequal response of the calorimeter to electrons and hadrons. The constant term is most significant at high energies. The third term is due to electronic noise and pile-up.

In the barrel and end-cap regions, hadronic calorimetry with an energy resolution of  $\frac{\Delta E}{E} = \frac{50\%}{\sqrt{E}} \oplus 5\%$  should be sufficient to meet the goals of the ATLAS detector. In the forward region, an energy resolution of  $\frac{\Delta E}{E} = \frac{100\%}{\sqrt{E}} \oplus 10\%$  should be adequate.

The hadronic barrel calorimeter is the only part of the calorimetry system which is not based on an absorber/liquid argon scheme. It will consist of scintillating tile, with steel as showering material. The tiles will be staggered in depth and oriented perpendicular to the colliding beams.

The hadronic end-cap calorimeter will consist of copper absorbers, with liquid argon as the ionization material. It will cover a range of  $1.5 \leq |\eta| \leq 3.2$ . Each end-cap consists of two wheels of similar construction. Each wheel is made of sheets of copper absorber, separated by gaps for the liquid argon.

### 4.3 The Muon System

The toroidal magnet configuration of ATLAS allows the muon identification and triggering to take place entirely outside of the calorimetry. Because the toroidal system will itself provide a measurement of momentum, the muon detection and triggering system is capable of operating up to the design luminosity of the LHC,  $10^{34} \text{ cm}^{-2}\text{s}^{-1}$ , and above.

The superconducting air-core toroid system is designed to produce a large-volume field with an open structure giving easy access for the installation of muon detectors. The barrel magnet, covering the central region up to  $|\eta| = 1.2$ , provides a magnetic field length of 3 Tm. This magnet consists of eight separate superconducting coils assembled as an axially symmetric array around the 10 meter diameter calorimeter barrel. Each coil is of a flat “race track” configuration, extending over a surface area of  $26 \times 5 \text{ m}^2$ . The coil is made of two single “pancakes” wound and clamped rigidly on both sides of a cold solid plate which acts as a central web to contain the internal forces imposed on the conductor. The pancakes are made of 50 turns of aluminum-stabilized rectangular conductor.

The forward regions are covered by two smaller end-cap toroids, which are designed to extend the coverage of the superconducting magnet system to about  $|\eta| = 3$ . These end-cap toroids will provide a magnetic field length of 8 Tm at  $|\eta| = 2.8$ . Like the barrel, each end-cap toroid consists of eight coils. The end-caps fit inside the barrel, the coils of the end-cap fitting between the coils of the barrel at the same radius [6].

A muon track is always measured in three “points”, from which the momentum can be determined. In the barrel, one point is in front, one behind, and one in the middle of the magnetic field region. In the end-caps, one point lies in front, and two lie behind the magnet. In the ATLAS detector, each point will be represented by a number of tracking chamber layers, forming a superlayer. The tracking system will provide a coordinate measurement in the bending plane with a resolution of  $100 \mu\text{m}$  or better per superlayer. Figure 4.6 shows the location of the muon tracking chambers.

In the barrel region, the muon chambers are arranged in cylindrical shells, concentric with the beam axis. Each chamber consists of two multilayers of drift

tubes. Most of the barrel chambers are rectangular in shape. In the end-cap region, the muon chambers are mounted vertically. Neighbouring chambers will overlap for full azimuthal coverage. The end-cap chambers are of trapezoidal shape.

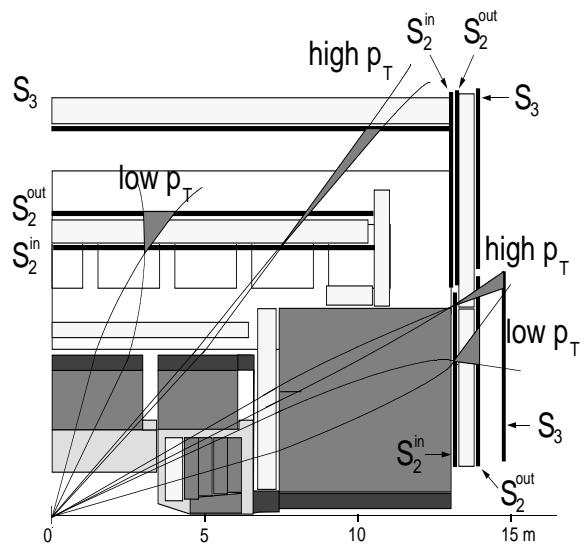

A separate muon detector system is used for triggering. For Higgs searches and B-physics, a high single-muon trigger efficiency is required. The trigger scheme is based on a coincidence logic, to combine the muon trigger with the other subdetector triggers for the same bunch-crossing. The muon trigger system uses two types of detectors: Resistive Plate Chambers (RPCs), and Thin Gap Chambers (TGCs). The same system also provides the second-coordinate measurement necessary for pattern recognition and momentum reconstruction.

The muon trigger system in both the barrel and end-cap regions consists of two stations of detectors [18]. The first station ( $S_2$ ) is split into two substations, each of which is made of two layers of strip detectors. The second station ( $S_3$ ) consists of three layers. A schematic diagram of the locations of the muon trigger stations is shown in Figure 4.7.

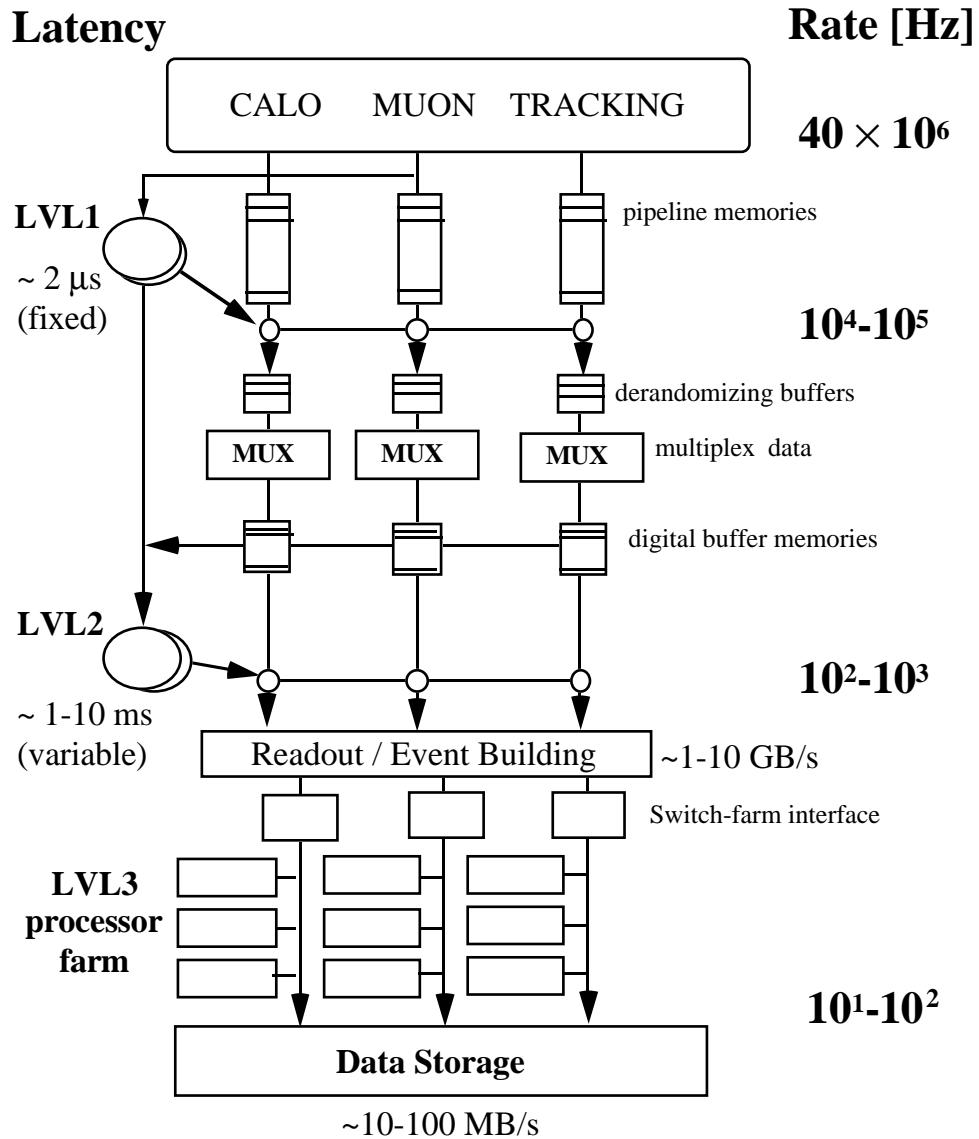

## 4.4 Triggering

Because most of the collisions that take place will not be ones that are interesting in terms of physics content, many of the bunch-crossings will be discarded. In order to accomplish this, each bunch-crossing will be subject to tests which determine if the bunch-crossing warrants further analysis or not. Such tests involve checking to see if certain particles and/or energies were detected. Each of these tests is called a trigger condition. The ATLAS trigger architecture is shown in Figure 4.8. The first rough check that takes place is called the Level 1 trigger.

Figure 4.6: Side view of the detector, showing the position of the muon chambers (taken from the ATLAS Technical Proposal, 1994).

Figure 4.7: Schematic of the muon trigger in the barrel and end-cap (taken from the ATLAS Technical Proposal, 1994).

The design LHC bunch-crossing frequency is 40 MHz. The latency of the Level 1 trigger will be about  $2.5 \mu\text{s}$ , during which time the data from all detectors will be stored in analog or digital pipeline memories until the first-level decision is made. The latency of the Level 1 trigger is the amount of time that elapses from when the LHC bunches cross until the trigger decision reaches the front-end electronics. The Level 1 trigger is expected to select events at a mean rate of about 100 kHz. This means that the readout system has on average  $10 \mu\text{s}$  to read data from the front-end electronics before the arrival of the next trigger accept. The Level 1 trigger will be determined by the calorimetry and/or the muon system information.

A second-level trigger will further reduce the rate, by demanding additional event signatures [19]. The inner detector may be used to achieve the desired background reduction, by locating tracks and determining their  $p_{\text{T}}$ . The Level 2 trigger architecture is based on the use of Regions of Interest. The regions of the detector containing interesting features (such as high- $p_{\text{T}}$  electromagnetic clusters (electrons/photons), jets or muons) are identified by the Level 1 trigger system. The Level 2 trigger then accesses and processes data from only these regions, which is a small fraction of the total detector data. The Level 2 trigger is designed to have an input rate of up to 100 kHz, and an output rate of 1 kHz.

The third-level trigger will perform the final event selection and data reduction prior to mass storage. Event selection for calibration and physics analysis, started at the second level, will be refined at the third level. In order to achieve full event analysis, an event builder will merge all of the data into complete events. The Level 3 trigger could use fully calibrated data and run offline-type algorithms.

Figure 4.8: The ATLAS three-level trigger architecture (taken from the ATLAS Technical Proposal, 1994).

# CHAPTER 5

## Calorimeter Electronics

This chapter presents an overview of the front-end readout electronics for ATLAS calorimetry. In particular, the scheme of pipelining detector signals is discussed.

### 5.1 Front-End Electronics

It is intended that the readout electronics have a 16-bit dynamic range. The dynamic range of the readout system is determined by the energy deposited in the calorimeter. It is estimated that a single calorimeter cell will experience a maximum energy deposit of 2 TeV. The requirement of a 16-bit dynamic range dictates a least count of 32 MeV. This is smaller than the expected preamplifier noise.

For the calorimeter components which utilize liquid argon, the front-end electronics begin with electrodes which collect the signals from the liquid. Printed circuit motherboards will combine the signals from 3 or 4 electrodes to form single readout channels. The motherboards also hold the cryogenic preamplifiers and distribute calibration signals.

Figure 5.1 shows the drift current versus time for an ionization calorimeter, and the response of a bipolar shaper with a shaping time<sup>1</sup> of 20 ns. Calibration circuits provide a precise pulse, simulating the triangular signal from the detector,

---

<sup>1</sup>The shaping time is about half of the peaking time (5 to 100%) for a triangular signal from the detector, and is defined as the peaking time for a delta pulse [20].

and allow precise measurements of the amplitude and timing for each channel. The calibration signal must have a very sharp edge (about 1 ns) and an accurate initial value. The decay time should be equal to the electron drift time (about 400 ns).

The purpose of the ASIC (Application Specific Integrated Circuit) shaper chips is to clip the long (400 ns) decay of the detector signals, and to optimize the signal-to-noise ratio. The shaping time is chosen to minimize the total noise, which is a combination of electronic noise and pile-up noise. This requires shaping times of between 20 and 50 ns for the various calorimeters at full luminosity. A multiple sampling technique (combining 3 to 5 samples) can be used to provide an optimum noise response [21].

Preamplifiers amplify the small calorimeter signals to minimize the noise from pick-up and from the subsequent stages. The preamplifiers determine the ultimate noise performance of the readout system, which must be optimized in order to achieve good resolution at low energy [6].

In the barrel region, noise considerations require that the liquid argon preamplifiers and calibration circuits be located within the cryostat. Silicon preamplifiers have been shown to be radiation hard, and reliable at cryogenic temperatures. Motherboards will be mounted directly on the calorimeter. Feed-throughs will carry the calorimeter signals through the cryostat walls. The preamplified signals will then be transferred to signal shaping electronics which will be placed as close as possible to the feed-throughs. In the end-cap regions, high radiation levels and a lack of space require that the preamplifiers be located outside of the cryostat, approximately 5 meters away. This is called the “0T” scheme, because there will be no transistors within the cryostat. The noise performance is comparable to levels achieved with cryogenic silicon preamplifiers.

Figure 5.1: (a) Drift current versus time for an ionization calorimeter; (b) Response of a bipolar shaper with a shaping time of 20 ns. The dots indicate the beam crossings. (Taken from the ATLAS Technical Proposal, 1994.)

A dual-range scheme is employed in order to obtain a 16-bit dynamic range while using a readout system capable of only a 13-bit resolution. The shapers will split the signals, and amplify one of the split signals by a factor of about 16, to obtain a low gain channel. The other unamplified split signal will be a high gain channel. The shaper chips will each be responsible for eight calorimeter channels, and will be mounted directly on the pipeline boards.

A trigger tower is formed by summing the signals from a group of calorimeter cells. The shaper circuits will provide some of the analog sums required to form the Level 1 trigger towers, because they will be assigned to adjacent calorimeter cells in the same longitudinal depth. The pipeline boards will transmit the sums to a Level 1 trigger summation board, for further summing to form the trigger towers.

## 5.2 Readout Electronics

The readout electronics are responsible for forming the Level 1 trigger sums, storing the analog signals until a Level 1 trigger accept, and digitizing the accepted events.

It is intended to use a common readout technology for the barrel, end-cap, and forward calorimeter subsystems. This will reduce development efforts and improve integration with a uniform, cost effective architecture.

In order to provide a deadtime-free Level 1 trigger, the readout electronics for all of the calorimeter subsystems must sample the signals from each calorimeter cell at the LHC bunch-crossing rate of 40 MHz. A combination of these signals is sent to the Level 1 trigger. The latency of the ATLAS Level 1 trigger will be about  $2.5\ \mu\text{s}$ , so the individual calorimeter signals must be stored temporarily in a pipeline until a decision from the Level 1 processor has been received. The pipeline will have 256

storage cells (capacitors) per input channel. About 100 storage cells will be occupied by data which are awaiting trigger decisions, and the other 156 cells will form a buffer containing accepted data which are awaiting digitization.

If a bunch-crossing is selected by the Level 1 trigger as being desirable, the calorimeter signals are digitized and then processed. The energy deposition, timing, and pile-up correction are extracted from the signals. This information is then passed on to the next level of triggering, which is the Level 2 trigger.

As mentioned previously, the front-end electronics are located on the detector. In order to minimize data transmission, the Level 1 trigger signals and the data extraction are done on the detector also.

A 16-bit dynamic range, with a sampling frequency of 40 MHz, is not easily obtained using current technology. To meet these criteria, two independent approaches are being studied.

### 5.3 Digital Pipeline Approach

One readout scheme being studied is a digital pipeline. This involves digitizing the signals from individual detector elements for each bunch-crossing. The data would then be stored in a digital memory until a decision is made by the Level 1 trigger.

The advantage of this approach is that the analog signals would be digitized immediately, before they are degraded by the noise of the systems. This could be done very close to the calorimeter, and so very little resolution would be lost due to noise.

The disadvantage to a digital pipeline is that the digitizer must operate at

a very high speed, since the sampling frequency is 40 MHz. This is difficult to accomplish with a 16-bit dynamic range. Range compression schemes may be used together with 10-bit or 11-bit ADCs. Input signals, with a dynamic range of 15-16 bits, are compressed and digitized at sampling frequencies up to 80 MHz. The resulting 10-bit data are linearized and expanded to the full 16-bit dynamic range by means of a look-up table containing the inverse transfer function of the detector-electronic chain. This provides an absolute calibration for each individual channel.

An example of a digital pipeline approach is the Front-End and Readout Microsystem (FERMI) system, developed as RD16 [22]. This is a complete readout system which incorporates into a single multichip module a dynamic range compressor, an ADC, non-linearity correction, generation of Level 1 trigger data, digital signal processing, data buffering, and a local controller [6].

An amplifier with four ranges of gain will process the detector signals, which have a dynamic range of up to 16 bits. The resulting analog signals are converted to digital signals by 10-bit ADCs. Prototype digitizers have operated at rates greater than 40 MHz. The 10-bit data are then linearized and re-expanded to 16 bits. Each FERMI module is expected to be responsible for 8 or 16 detector channels.

## 5.4 Analog Pipeline Approach

Another type of system being considered is an analog pipeline. This approach involves storing the analog charge from each detector element in capacitors, while a Level 1 trigger decision is being made. The signals from the successive bunch-crossings would be stored in different capacitors. The capacitor addresses associated with each bunch-crossing would be recorded digitally. If the Level 1 trigger accepts the bunch-crossing,

then the signals from that bunch-crossing are digitized. Once the data have been read, the capacitors may be overwritten by a subsequent bunch-crossing. Since only a small percentage of the bunch-crossings are accepted, this method greatly reduces the required digitization rate. Thus, an analog pipeline system has the advantage of placing a reasonable demand on the digitizing electronics.

The disadvantage of this approach is that the analog signals must be stored for several microseconds, with high precision. Since the electronics will be in a noisy environment, this will result in significant noise pickup, which will reduce the dynamic range.

A prototype analog pipeline readout module is currently being tested at the University of Alberta. The readout module and the tests performed form the topic of this thesis.

# CHAPTER 6

## An Analog Pipeline Readout System

As discussed above, an analog pipeline is one of the approaches being considered for the readout electronics of the ATLAS calorimeters. The entire readout system must have a 16-bit dynamic range, with a 12-13 bit accuracy. Also, it must have low power requirements, low cost, operate with no deadtime, and be compact, reliable and radiation hard.

### 6.1 Pipeline Readout Board

It will be challenging to obtain a digitization rate at the LHC bunch-crossing rate of 40 MHz with a greater than 15-bit dynamic range. However, it is possible to use a digitization rate of only 100 kHz by storing the data in analog form until a Level 1 trigger accept.

#### 6.1.1 Switched Capacitor Array Chip

One method of pipelining analog detector signals is through the use of a switched capacitor array (SCA) [23]. This technique provides fast sampling speeds and a wide dynamic range while requiring low cost and low power. Such an approach has been used successfully in the ZEUS experiment [24].

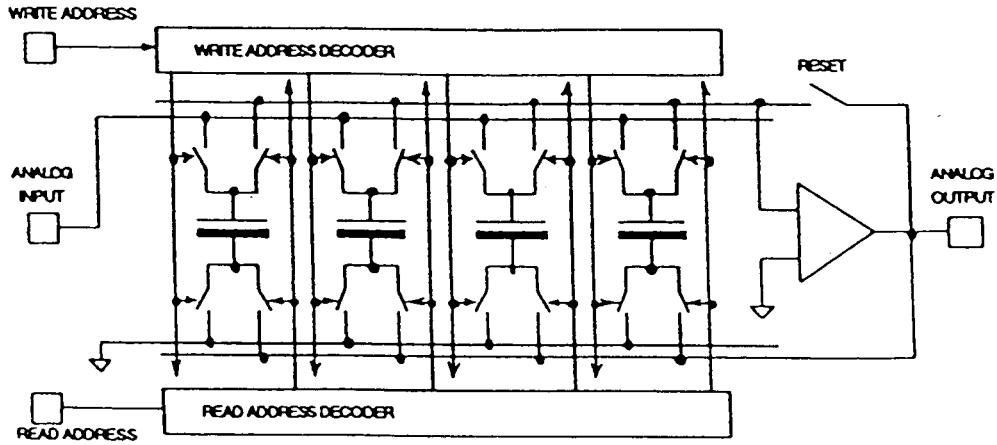

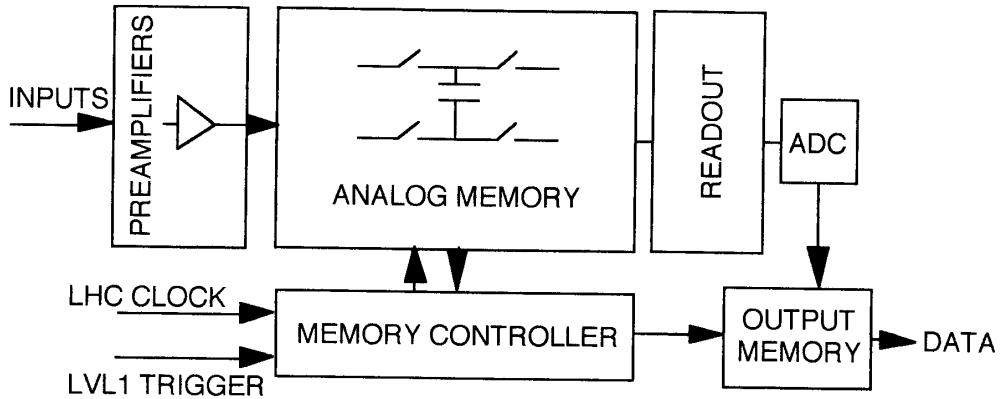

A simplified block diagram of an analog memory cell structure is shown in Figure 6.1. The switched capacitor array chips were originally designed at the Lawrence Berkeley Laboratory [25], and were fabricated by Orbit Semiconductor, Inc., in Sunnyvale, California. The SCA memory consists of 16 parallel channels, each of which has 256 sample-and-hold cells (capacitors). Each sample-and-hold cell consists of a complementary metal oxide semiconductor (CMOS) transmission gate and a 0.7 pF double-polysilicon capacitor. A reference voltage is applied to the bottom plate of each capacitor. The difference between the input signal and the applied reference voltage is therefore the voltage stored on each capacitor.

The SCA chip is addressed externally. The address decoder in the SCA chip uses a break-before-make action, which ensures that an analog signal cannot be split between capacitors. In a given channel, the capacitors can be addressed in any order. Also, a signal can be retrieved from one capacitor while a second signal is being stored in another capacitor, in the same channel, by using separate read and write buses. Thus, the analog pipeline allows for deadtime free operation.

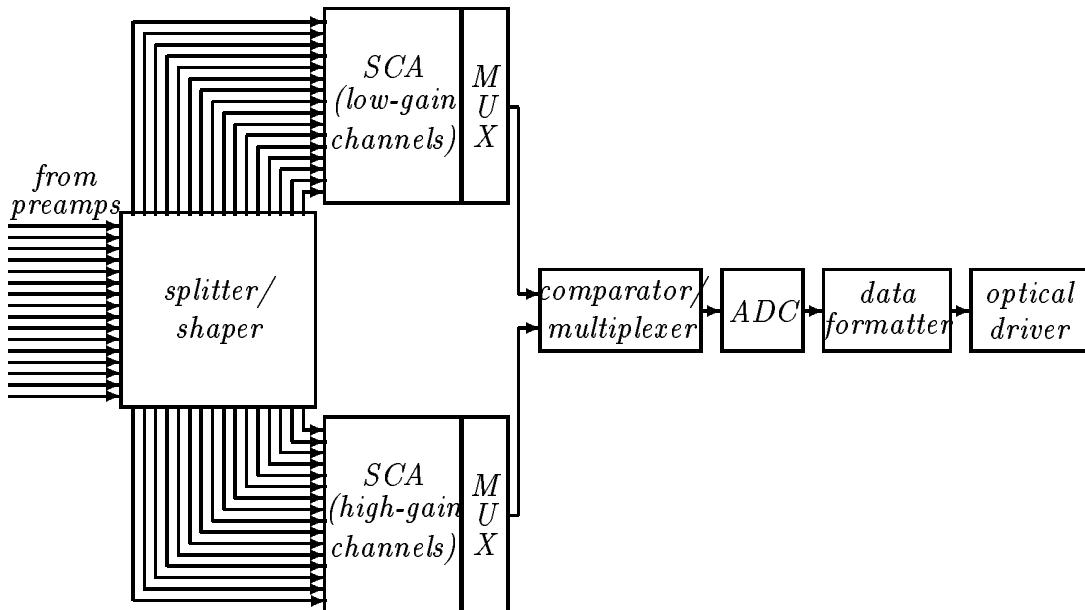

### 6.1.2 Readout System Design

A schematic diagram of the readout system design is shown in Figure 6.2. The readout system design consists of a dual-range scheme with SCA chips, followed by commercial ADCs. The signals from the calorimeter preamplifiers will be split into two gain scales, and processed by shapers with a greater than 12-bit dynamic range, before being sampled at 40 MHz. This will facilitate the required greater than 15-bit dynamic range. Also, the splitting will reduce the digitization requirements, and thus allow for the use of commercial ADCs. The pulse shaping time is optimized to minimize the effects of noise and pile-up from crossings near in time, but will still

Figure 6.1: A simplified block diagram of an analog memory cell structure (taken from M. Levi *et al.*, “A Switched Capacitor Array Based System for High-Speed Calorimetry”, 1991).

preserve the advantages of the calorimeter speed.

There are in fact two types of pile-up. Pile-up in the calorimeter occurs when particles from different collisions pass through the same cells of the calorimeter. This happens because many collisions take place during each bunch-crossing, at essentially the identical time. Pile-up in the calorimeter can not be avoided, but can be reduced by using small calorimeter cells. Pile-up due to the readout electronics is a result of two distinct signals from a calorimeter cell occurring very close to each other in time. In order to minimize this type of pile-up, the calorimeter signals are shaped as quickly as possible.

The stored calorimeter signals are only digitized if the Level 1 trigger accepts them. The digitization time is about  $10 \mu\text{s}$  per sample on average. The high gain signals are compared to the reference voltage before digitization. It is expected that

16 channels will be multiplexed into 12-bit 10 MHz ADCs, and five samples per channel will be digitized. This will reduce the number of ADCs, and hence the cost and power requirements. The SCA addresses and the digital data are then dumped into Level 2 buffers.

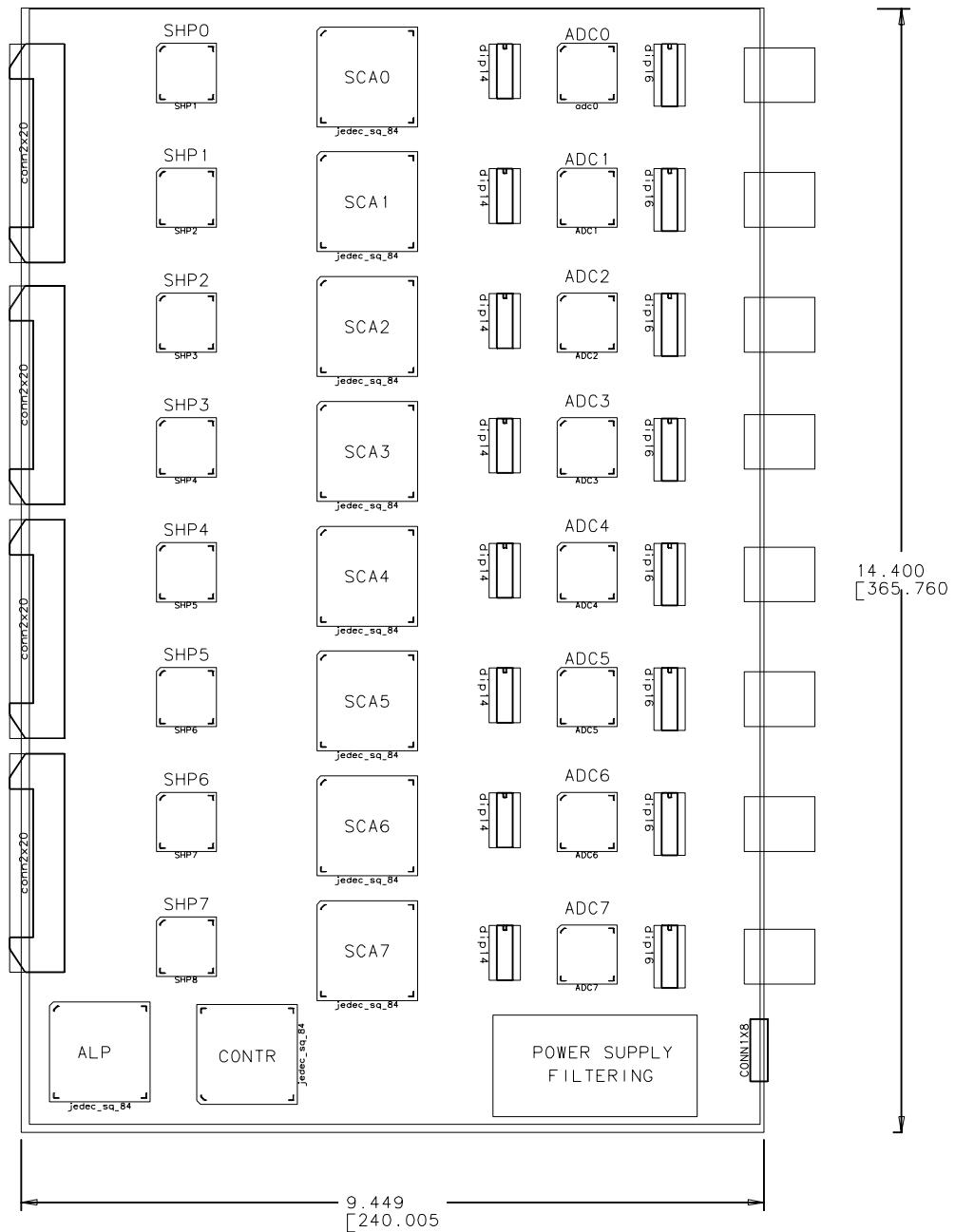

Figure 6.2: Schematic diagram of 16 channels of the readout system design. The timing, control logic, and Level 1 trigger connections are not shown.

Because signals from the electromagnetic calorimeter are formed slowly compared to the bunch-crossing time, it is necessary to readout several calorimeter samples for each Level 1 trigger accept. The number of samples which are read out can be easily changed. Five samples should be sufficient to reconstruct the time and energy

of each signal pulse. Also, the use of five samples should provide adequate discrimination against large pile-up, electronic noise, and signal overlap. It is expected that the required total rms (root mean square) time accuracy will be about 1 ns.

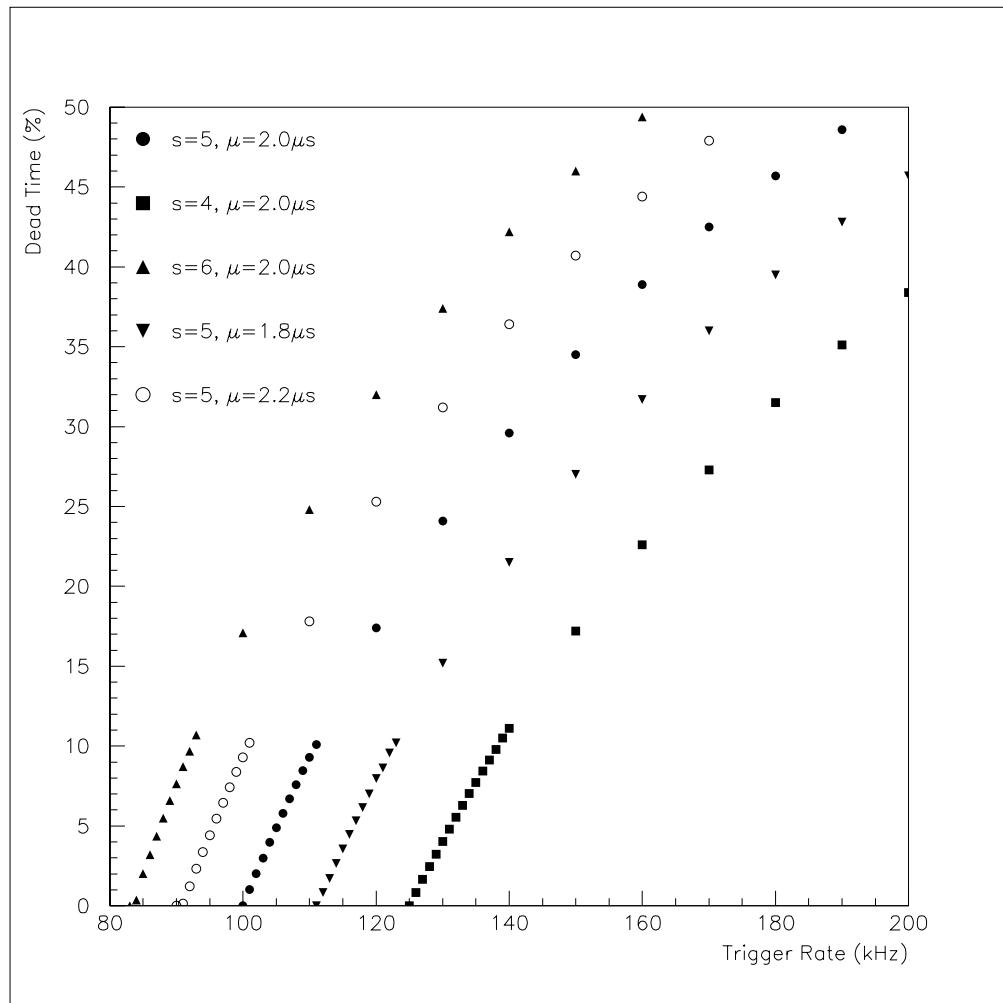

## 6.2 Pipeline Controller

By allowing simultaneous read and write operations, and the ability to write to non-sequential locations in the SCA, one can obtain deadtime free performance of the pipeline system. Figure 6.3 shows a plot of deadtime versus trigger rate, for different numbers of samples and different readout times. 100 pipeline storage cells per channel are required for a  $2.5 \mu\text{s}$  Level 1 trigger latency and a 40 MHz bunch-crossing frequency. By keeping track of the SCA addresses, one can obtain deadtime free operation provided that the rate of Level 1 accepts does not greatly exceed 100 kHz. Deadtime would occur if data were stored in sequentially located capacitors.

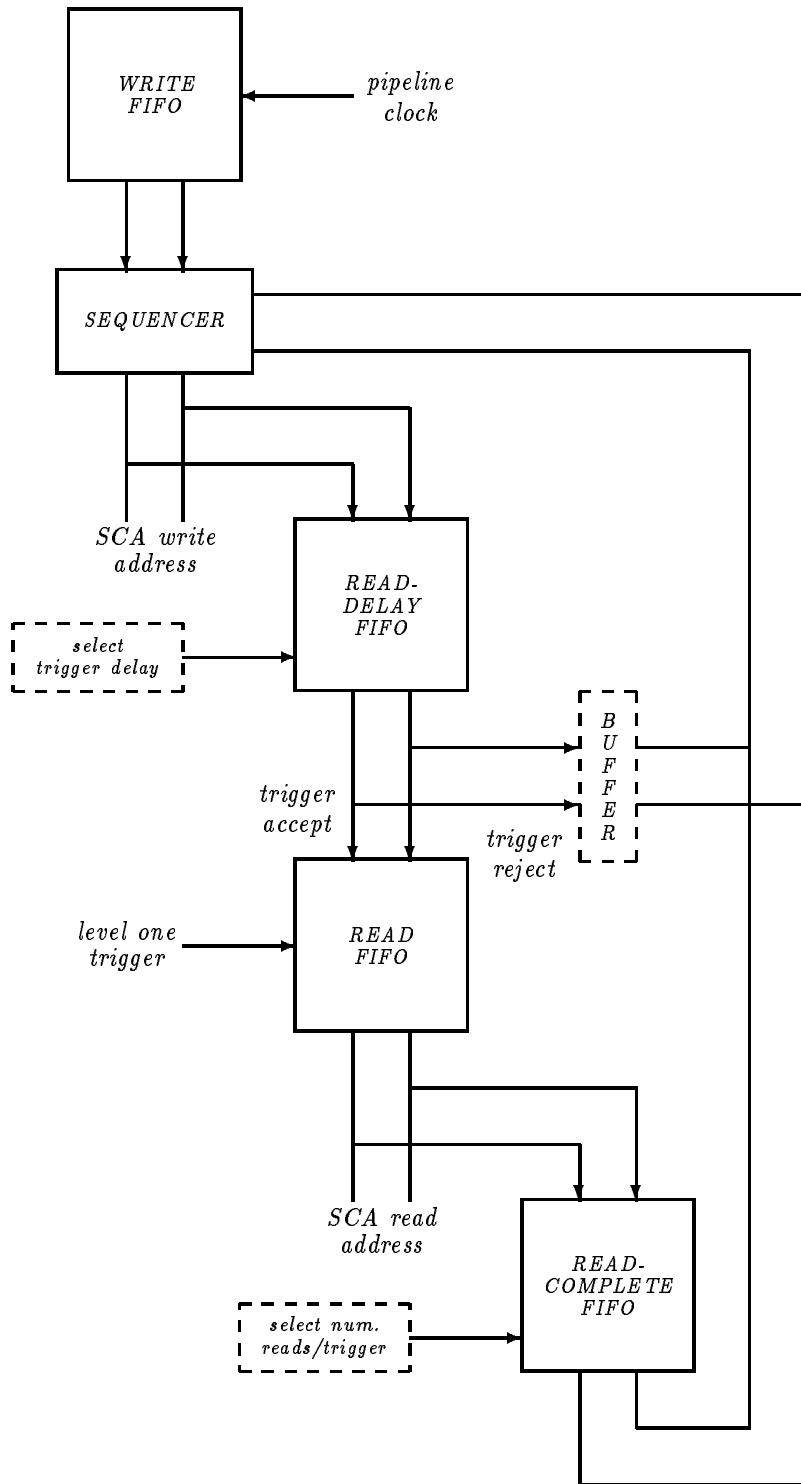

An address list processor (ALP) circuit [26] on the pipeline module is used to control the SCA chip and hence manage the capacitor addresses. The ALP will tag each address as empty, pending Level 1 trigger, or pending readout. In essence, the ALP circuit substitutes movement of analog data (stored signal) for digital data (address of stored signal) [27]. Figure 6.4 shows a block diagram of the address list processor design.

## 6.3 System Architecture

There are many factors taken into consideration when designing the readout architecture, including: minimizing the amount of electronics on the detector, dividing

Figure 6.3: Plot of deadtime (as a percentage) versus trigger rate (kHz), for different numbers of samples ( $s$ ) and different readout times ( $\mu$ ).

Figure 6.4: Block diagram of the address list processor design.