HDL2GDS is a set of sciprts designed to take HLD and produce an ASIC based on CMC's Artisan18.2.0 kit. To run these scripts you need to be part of the artisan group.

Copy the HDL2GDS design flow to your home directory:

% cd

% gunzip -c hdl2gds.tar.gz | tar xvf -

Add the following lines to your .cshrc file located in your home directory:

source /CMC/scripts/setenv.cds.03.csh

source /CMC/scripts/setenv.calibre.csh

source /CMC/scripts/setenv.synopsys.csh

setenv PATH /CMC/tools/synopsys/pt_U-2003.03-SP1/sparcOS5/syn/bin:${PATH}

Now re-source the .cshrc file (not required when you login again)

% source ~/.cshrc

Setup the flow (takes 10 to 20 mins):

% cd ~/hdl2gds

% setup.pl

HDL2GDS.pdf contains more detailed information on the flow. In the hdl/cmcuart/ directory is CMC's example UART design. To build a chip out of HDL description of the UART, type:

% hdl2gds.pl cmcuart > log.cmcuart &

Monitor log.cmcuart for any errors. HDL2GDS should take 15 minutes to build the chip. At the end of log.cmcuart you will find a summary of the time taken for each phase of the flow.

When complete, examine the synthesis reports in the syn/report/cmcuart/ directory. Their are four reports created:

uart_chip_area.rpt - contains the cell area in um2

uart_chip_port.rpt - contains port loading information

uart_chip_constraint.rpt - contains pass/fail constraint information (i.e. clock, area constraints)

uart_chip_timing.rpt - tells you if synthesis MET or VIOLATED your timing constraints

uart_chip_power.rpt - contains power information

From the timing report you will see that the cmcuart design has met timing and has a slack time of 14.64 ns. A positive slack time tells you that, in the worst case, the data arives 14.64 ns before clock and indicates you can clock your design faster. The reverse is somewhat true for negative slack times.

From the area report you will see that the cmcuart design takes 264,354 um2.

Now examine the static-timing analysis reports in the pt/report/cmcuart/ directory.

Note that these static-timing reports are based on extracted resistances and capacitances

from the physical design and thus are more

acurate than the timing report generated in the synthesis phase.

uart_chip_bottleneck.rpt - show the bottlenecks in your design

uart_chip_timing.rpt - tell you if the physical design MET or VIOLATED your timing constraints

uart_chip_constraint.rpt - contains constraint information

In the timing report, the "Path type: max" is related to setup time violations, which determine the design's minimum clock period and "Path type: min" is related to hold time violations. Note the the "max" slack time is 12.47 ns. It appears that the physical design did not do as good a good as synthesis predicited it could (or maybe it didn't try to hard when it noticed that it was already meeting timing).

Lets take a look at the design

% cd ~/hdl2gds/dfII/

% startCds -t cmosp18

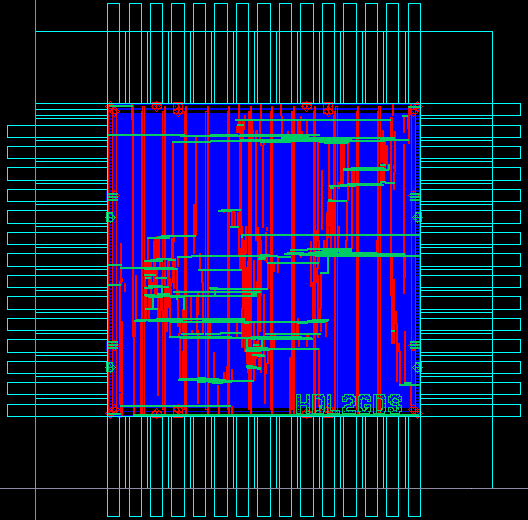

When Cadence opens, press F6, click on the "design" library so it is selected, then make sure uart_chip_cmcuart is selected and double click layout. When the layout comes up, press SHIFT+F. Explore your design.

Create a new release

% cd ~/hdl2gds/

% newrelease.pl cmcuart2

Copy the HDL files from hdl/cmcuart/ into /hdl/cmcuart2/

% cp hdl/cmcuart/* hdl/cmcuart2/

Copy the old contraints file over the newly created contraints file

% cp config_cmcuart.tcl config_cmcuart2.tcl

Edit the new constraints file config_cmcuart2.tcl and set the release and set the clock period to 12 ns:

set release cmcuart2

set clockPeriod 12

Now re-run synthesis by typing:

% hdl2gds.pl -run synth cmcuart2 > synth.cmcuart2 &

Monitor the synth.cmcuart2 log for any errors. When synthesis is complete for the cmcuart2

release compare its timing, area and power values to that of the original cmcuart release.

Now run the entire flow:

% hdl2gds.pl cmcuart2 > log.cmcuart2 &

Compare the synthesis timing, area and power results, located in the syn/report/cmcuart2/ directory, with the static-timing analyzer's results, located in the pt/report/cmcuart2/ directory.

Create a new release: cmcuart3

Copy the hdl files from hdl/cmcuart2/ to hdl/cmcuart3 and copy the config file

% cp hdl/cmcuart2/* hdl/cmcuart3/

% cp config_cmcuart2.tcl config_cmcuart3.tcl

Edit config_cmcuart3.tcl and set:

set release cmcuart3

We are going to take a closer look at the clock. Back in the cmcuart3 constraints

file (config_cmcuart3.tcl) change clkTreeSynthesisEn from 1 to 0:

set clkTreeSynthesisEn 0

Run the design through the flow:

% hdl2gds.pl cmcuart3 > log.cmcuart3 &

Compare the static timing results of cmcuart2 with that of cmcuart3. How long does the clock take to propagate to the register in the worst case?