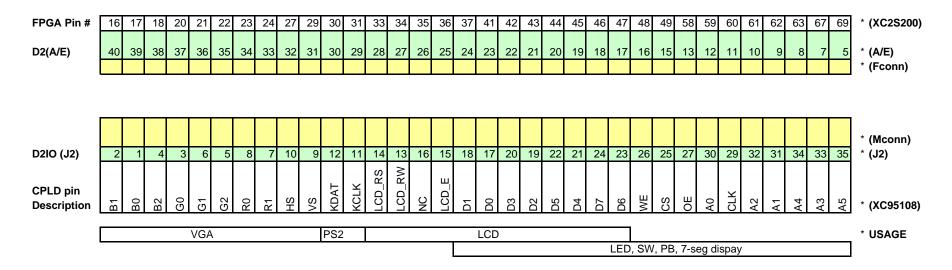

## HOW TO READ THIS SUMMARY - (top to bottom)

| Row<br>FPGA PIN<br>D2<br>D2IO<br>CPLD | Description<br>Represents the pin number of the XC2S200 FPGA on the D2 board.<br>FPGA pin # is routed to the D2 headers A and E on the edges of the D2 board.<br>When connected to the male header (J2) on the D2IO board, the pins are connected as shown in the above chart (vertically).<br>The pins of the J2 connector on the D2IO board ar ethen routed to the CPLD (bus controller) in the fasion described above.<br>The CPLD pins are static and cannot be changed (as far as you are concerned) so the pin descriptions are listed rather that the pin numbers. |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>*LEGEND</u>                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| XC2S200<br>A/E<br>Fconn<br>Mconn      | Spartan II FPGA - Main programmable device, located on the Digilab D2 development board.<br>I/O Ports A and E on the D2 board are mirrored to allow connection to 2 daughter boards. In EE480 we will use port E for I/O connectivity.<br>Female Connector<br>Male Connector                                                                                                                                                                                                                                                                                              |

- J2 PCB label found on the Digilab D2IO trainer daughter board. This connector mates with port E of the D2 board.

- **XC95108** Non-Volitile CPLD programmed to act as a bus controller for the D2IO hardware.

- **USAGE** Illustrates the target I/O device for associated pin description.

EXAMPLE: To map a logical port in your VHDL design to CS on the D2IO you would assign that logical port to pin # 49 using the constraints editor.